# Engineering Notebook

# VOLUME 1

# EE1308 Analog integrated circuits and its applications

A.V.Gokhale

Dr.Y.A.Gaidhani

### **DEPARTMENT OF ELECTRONICS ENGINEERING**

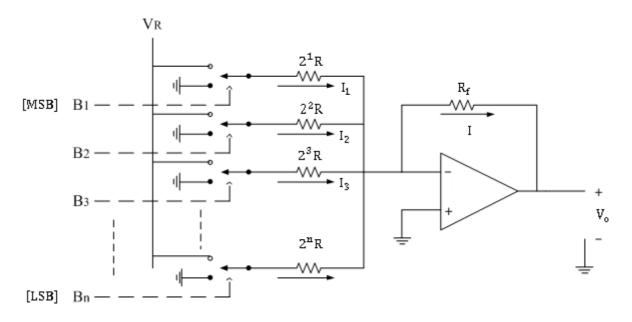

YESHWANTRAO CHAVANCOLLEGE OFENGINEERING, (AnautonomousinstitutionaffiliatedtoRashtrasantTukadojiMaharajNagpurUniversity,Nagpur)

NAGPUR– 441110

Copyright © 2012 Author/ s Name

All rights reserved.

ISBN:

## MESSAGE / MESSAGES

Insert message text here. Insert message text here.

## CONTENTS

| UN | Content                                           | Page |

|----|---------------------------------------------------|------|

|    |                                                   | no   |

| 1  | Differential Amplifier configurations             | 1    |

| 2  | Operational amplifier fundamentals                | 21   |

| 3  | Linear Applications of Operational Amplifier      | 43   |

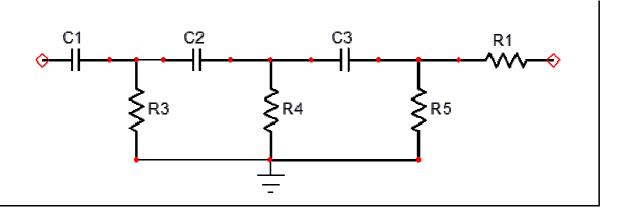

| 4  | Active Filters of Operational Amplifier           | 63   |

| 5  | Nonlinear Circuits And Waveform Generators        | 79   |

| 6  | Monolithic timer IC555 and D-A AND A-D CONVERTERS | 108  |

## ACKNOWLEDGMENTS

Insert acknowledgments text here. Insert acknowledgments text here.

i

# UNIT-1

# Differential Amplifier configurations

**Q.1.** Explain how the differential amplifier is developed and its different configurations?

#### Answer:

The operational amplifier is a direct-coupled high gain amplifier usable from 0 to over 1MH Z to which feedback is added to control its overall response characteristic i.e. gain and bandwidth. The op-amp exhibits the gain down to zero frequency.

Such direct coupled (dc) amplifiers do not use blocking (coupling and by pass) capacitors since these would reduce the amplification to zero at zero frequency. Large by pass capacitors may be used but it is not possible to fabricate large capacitors on a IC chip. The capacitors fabricated are usually less than 20 pf. Transistor, diodes and resistors are also fabricated on the same chip.

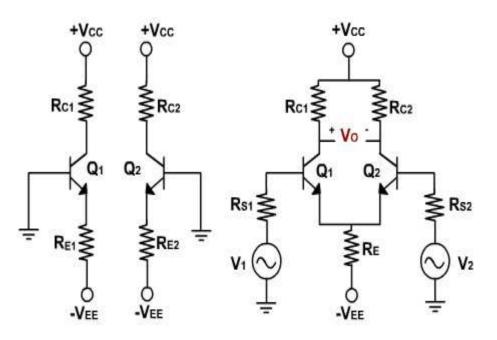

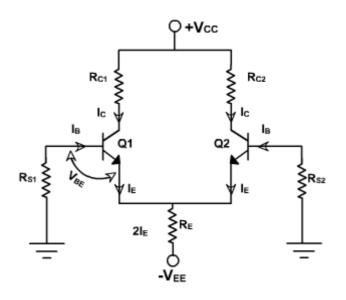

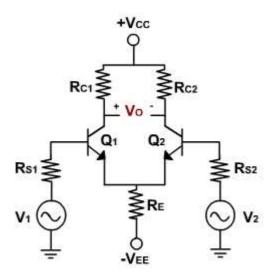

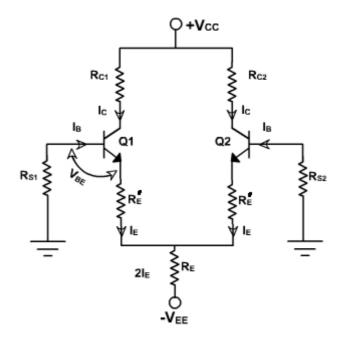

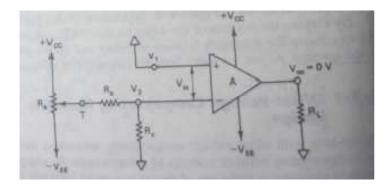

Differential amplifier is a basic building block of an op-amp. The function of a differential amplifier is to amplify the difference between two input signals.Let us consider two emitter-biased circuits as shown in **fig. 1.1**.

**Figure 1.1 Differential Amplifier**

The two transistors  $Q_1$  and  $Q_2$  have identical characteristics. The resistances of the circuits are equal, i.e.  $R_{E1} = R_{E2}$ ,  $R_{C1} = R_{C2}$  and the magnitude of  $+V_{CC}$  is equal to the magnitude of  $-V_{EE}$ . These voltages are measured with respect to ground.

To make a differential amplifier, the two circuits are connected as shown in **fig. 1.1**. The two  $+V_{CC}$  and  $-V_{EE}$  supply terminals are made common because they are same. The two emitters are also connected and the parallel combination of  $R_{E1}$  and  $R_{E2}$  is replaced by a resistance  $R_E$ . The two input signals  $v_1 \& v_2$  are applied at the base of  $Q_1$  and at the base of  $Q_2$ . The output voltage is taken between two collectors. The collector resistances are equal and therefore denoted by  $R_C = R_{C1} = R_{C2}$ .

Ideally, the output voltage is zero when the two inputs are equal. When  $v_1$  is greater then  $v_2$  the output voltage with the polarity shown appears. When  $v_1$  is less than  $v_2$ , the output voltage has the opposite polarity.

The differential amplifiers are of different configurations.

The four differential amplifier configurations are following:

- 1. Dual input, balanced output differential amplifier.

- 2. Dual input, unbalanced output differential amplifier.

- 3. Single input balanced output differential amplifier.

- 4. Single input unbalanced output differential amplifier.

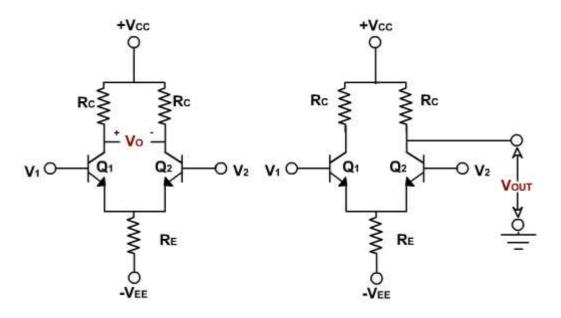

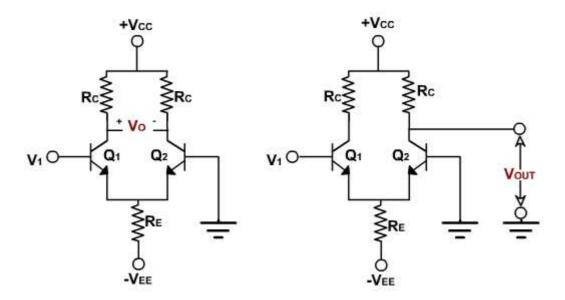

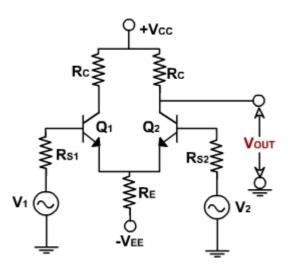

Figure 1.2 Dual input Balanced output and Dual input Unbalanced output Differential Amplifier

Figure 1.3 Single input Balanced output and Single input Unbalanced output Differential Amplifier

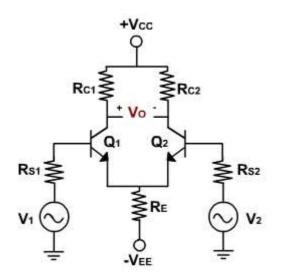

These configurations are shown in **fig. 1.2 and 1.3**, and are defined by number of input signals used and the way an output voltage is measured. If use two input signals, the configuration is said to be

dual input, otherwise it is a single input configuration. On the other hand, if the output voltage is measured between two collectors, it is referred to as a balanced output because both the collectors are at the same dc potential w.r.t. ground. If the output is measured at one of the collectors w.r.t. ground, the configuration is called an unbalanced output.

A multistage amplifier with a desired gain can be obtained using direct connection between successive stages of differential amplifiers. The advantage of direct coupling is that it removes the lower cut off frequency imposed by the coupling capacitors, and they are therefore, capable of amplifying dc as well as ac input signals.

# **Q.2.** Derive the expressions for DC analysis of Dual Input, Balanced Output Differential Amplifier.

#### Answer:

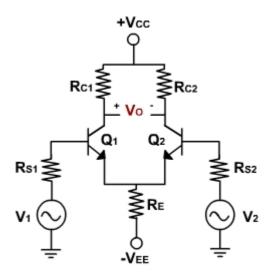

The circuit of Dual Input, Balanced Output Differential Amplifieris shown in **fig. 1.4**,  $v_1$  and  $v_2$  are the two inputs, applied to the bases of  $Q_1$  and  $Q_2$  transistors. The output voltage is measured between the two collectors  $C_1$  and  $C_2$ , which are at same dc potentials.

Figure 1.4 Dual input Balanced output Differential Amplifier

#### **D.C.** Analysis:

To obtain the operating point ( $I_{CC}$  and  $V_{CEQ}$ ) for differential amplifier dc equivalent circuit is drawn by reducing the input voltages  $v_1$  and  $v_2$  to zero as shown in **fig. 1.5**.

Figure 1.5 DC equivalent circuit of Dual input Balanced output Differential Amplifier

The internal resistances of the input signals are denoted by  $R_S$  because  $R_{S1} = R_{S2}$ . Since both emitter biased sections of the different amplifier are symmetrical in all respects, therefore, the operating point for only one section need to be determined. The same values of  $I_{CQ}$  and  $V_{CEQ}$  can be used for second transistor  $Q_2$ .

Applying KVL to the base emitter loop of the transistor Q<sub>1</sub>.

$$\begin{split} &\mathsf{R}_{\mathsf{S}} \; \mathsf{I}_{\mathsf{B}} + \mathsf{V}_{\mathsf{B}\mathsf{E}} + 2 \; \mathsf{I}_{\mathsf{E}} \; \mathsf{R}_{\mathsf{E}} = \mathsf{V}_{\mathsf{E}\mathsf{E}} \\ &\mathsf{But} \; \; \mathsf{I}_{\mathsf{B}} \; = \; \frac{\mathsf{I}_{\mathsf{E}}}{\beta_{\mathsf{do}}} \; \; \mathsf{and} \; \mathsf{I}_{\mathsf{C}} \approx \mathsf{I}_{\mathsf{E}} \\ &\therefore \mathsf{I}_{\mathsf{E}} \; = \; \mathsf{I}_{\mathsf{C}} \; = \; \frac{\mathsf{V}_{\mathsf{E}\mathsf{E}} - \mathsf{V}_{\mathsf{B}\mathsf{E}}}{2\mathsf{R}_{\mathsf{E}} + \mathsf{R}_{\mathsf{S}} \; / \; \beta_{\mathsf{do}}} \qquad (\mathsf{E}\text{-}1) \\ &\mathsf{V}_{\mathsf{B}\mathsf{E}} = \; 0.6 \; \mathsf{V} \; \; \mathsf{for} \; \; \mathsf{S}_{\mathsf{i}} \; \; \mathsf{and} \; \; 0.2 \; \mathsf{V} \; \mathsf{for} \; \; \mathsf{G}_{\mathsf{e}}. \\ &\mathsf{Generally} \; \; \frac{\mathsf{R}_{\mathsf{S}}}{\beta_{\mathsf{do}}} << \; 2\mathsf{R}_{\mathsf{E}} \; \; \mathsf{because} \; \; \mathsf{R}_{\mathsf{S}} \; \mathsf{is the internal resistance of input signal} \\ &\therefore \mathsf{I}_{\mathsf{E}} \; = \; \mathsf{I}_{\mathsf{C}} = \; \frac{\mathsf{V}_{\mathsf{E}\mathsf{E}} - \mathsf{V}_{\mathsf{B}\mathsf{E}}}{2\mathsf{R}_{\mathsf{E}}} \end{split}$$

The value of  $R_E$  sets up the emitter current in transistors  $Q_1$  and  $Q_2$  for a given value of  $V_{EE}$ . The emitter current in  $Q_1$  and  $Q_2$  are independent of collector resistance  $R_C$ .

The voltage at the emitter of  $Q_1$  is approximately equal to  $-V_{BE}$  if the voltage drop across R is negligible. Knowing the value of  $I_C$  the voltage at the collector  $V_C$  is given by

$$V_C = V_{CC} - I_C R_C$$

and  $V_{CE} = V_C - V_E$

$$= V_{CC} - I_C R_C + V_{BE}$$

$$V_{CE} = V_{CC} + V_{BE} - I_C R_C \qquad (E-2)$$

From the two equations  $V_{CEQ}$  and  $I_{CQ}$  can be determined. This dc analysis applicable for all configurations of differential amplifier.

# **Q.3.** Derive the expressions for AC analysis of Dual Input, Balanced Output Differential Amplifier.

#### Answer:

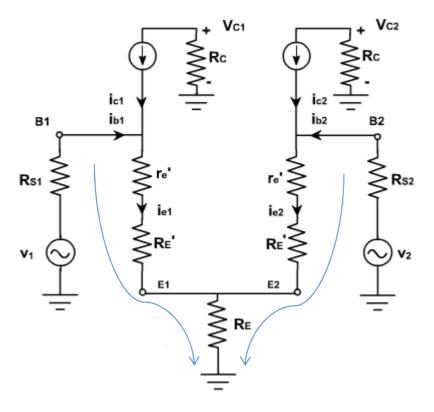

The circuit is shown in **fig. 1.6**  $v_1$  and  $v_2$  are the two inputs, applied to the bases of  $Q_1$  and  $Q_2$  transistors. The output voltage is measured between the two collectors  $C_1$  and  $C_2$ , which are at same dc potentials.

Figure 1.6 Dual input Balanced output Differential Amplifier

#### A.C. Analysis : Differential Voltage GainAd

After performing the dc analysis we obtain the operating point of the two transistors.

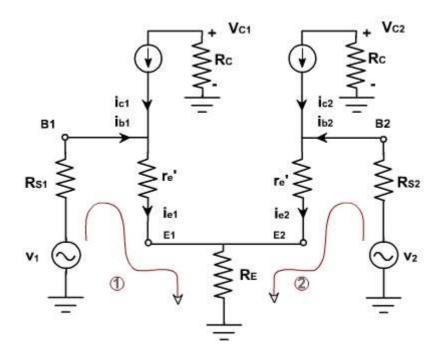

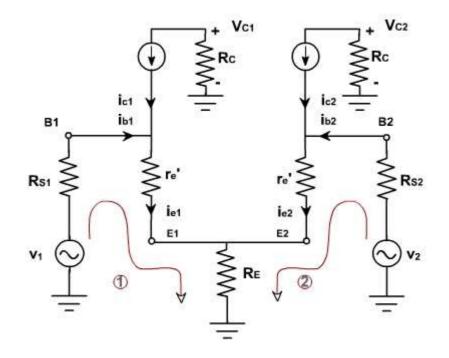

To find the voltage gain  $A_d$  and the input resistance  $R_i$  of the differential amplifier, the ac equivalent circuit is drawn using r-parameters as shown in **fig. 1.7**. The dc voltages are reduced to zero and the ac equivalent of CE configuration is used.

Figure 1.7 AC equivalent circuit of Dual input Balanced output Differential Amplifier

Since the two dc emitter currents are equal. Therefore, resistance  $r'_{e1}$  and  $r'_{e2}$  are also equal and designated by  $r'_e$ . This voltage across each collector resistance is shown 180° out of phase with respect to the input voltages  $v_1$  and  $v_2$ . This is same as in CE configuration. The polarity of the output voltage is shown in Figure. The collector  $C_2$  is assumed to be more positive with respect to collector  $C_1$  even though both are negative with respect to to ground.

Applying KVL in two loops 1 & 2.

$$v_1 = R_{S1} i_{b1} + i_{e1} r'_e + (i_{e1} + i_{e2}) R_E$$

$v_2 = R_{S2} i_{b2} + i_{e2} r'_e + (i_{e1} + i_{e2}) R_E$

Substituting current relations,

$$\begin{split} i_{b1} &= \frac{i_{e1}}{\beta}, \ i_{b2} = \frac{i_{e2}}{\beta} \\ V_1 &= \frac{R_{s1}}{\beta}, \ i_{e1} + r'_e, i_{e1} + R_E, (i_{e1} + i_{e2}) \\ V_2 &= \frac{R_{s2}}{\beta}, i_{e2} + r'_e, i_{e2} + R_E, (i_{e1} + i_{e2}) \end{split}$$

Again, assuming  $R_{S1}$  / b and  $R_{S2}$  / b are very small in comparison with  $R_E$  and  $r_e^{\prime}$  and therefore neglecting these terms,

Solving these two equations,  $i_{e1}$  and  $i_{e2}$  can be calculated.

$$\begin{split} i_{e1} &= \frac{(r_e + R_E) v_1 - R_E v_2}{(r_e' + R_E)^2 - R_E^2} \\ i_{e2} &= \frac{(r_e' + R_E) v_2 - R_E v_1}{(r_e' + R_E)^2 - R_E^2} \end{split}$$

The output voltage  $V_O$  is given by

$$\begin{split} V_{O} &= V_{C2} - V_{C1} \\ &= -R_{C} i_{C2} - (-R_{C} i_{C1}) \\ &= R_{C} (i_{C1} - i_{C2}) \\ &= R_{C} (i_{e1} - i_{e2}) \end{split}$$

Substituting  $i_{e1}$ , &  $i_{e2}$  in the above expression

$$v_{o} = R_{C} \left\{ \frac{(r_{e} + R_{E})V_{1} - R_{E}V_{2}}{(r'_{e} + R_{E})^{2} - R_{E}^{2}} - \frac{(r_{e} + R_{E})V_{2} - R_{E}V_{1}}{(r'_{e} + R_{E})^{2} - R_{E}^{2}} \right\}$$

$$= \frac{R_{C}(v_{1} - v_{2})(r'_{e} - 2R_{E})}{r'_{e}(r'_{e} + 2R_{E})}$$

Therefore,  $v_{o} = \frac{R_{C}}{r'_{e}}(v_{1} - v_{2})$  (E-1)

Thus a differential amplifier amplifies the difference between two input signals. Defining the difference of input signals as  $v_d = v_1 - v_2$  the voltage gain of the dual input balanced output differential amplifier can be given by

$$A_{d} = \frac{v_{c}}{v_{d}} = \frac{R_{c}}{r'_{e}} (E-2)$$

#### Differential Input Resistance: R<sub>i1</sub>andR<sub>i2</sub>

Differential input resistance is defined as the equivalent resistance that would be measured at either input terminal with the other terminal grounded. This means that the input resistance  $R_{i1}$  seen from the input signal source  $v_1$  is determined with the signal source  $v_2$  set at zero. Similarly, the input signal  $v_1$  is set at zero to determine the input resistance  $R_{i2}$  seen from the input signal source  $v_2$ . Resistance  $R_{s1}$  and  $R_{s2}$  are ignored because they are very small.

$$\begin{aligned} \mathsf{R}_{i1} &= \frac{\mathsf{V}_1}{\mathsf{i}_{b1}} \bigg|_{\mathsf{V}_2} = 0 \\ &= \frac{\mathsf{V}_1}{\mathsf{i}_{e1}/\beta} \bigg|_{\mathsf{V}_2} = 0 \end{aligned}$$

.

Substituting ie1,

$$R_{i1} = \frac{\beta r'_e(r'_e + 2R_E)}{r'_e + R_E}$$

Since  $R_E >> r'_e$

$\therefore r'_e + 2R_E >> 2R_E$

or  $r'_e + R_E >> R_E$

$\therefore R_{i1} = 2\beta r_e'$  (E-3)

Similarly,

$$R_{i2} = \frac{V_2}{i_{b2}} \bigg|_{V_1} = 0$$

$$= \frac{V_2}{i_{c2} / \beta} \bigg|_{V_1} = 0$$

$$R_{i2} = 2\beta r'_e \quad (E-4)$$

The factor of 2 arises because the  $r_e'$  of each transistor is in series.

#### Output Resistance: Ro1and Ro2

Output resistance is defined as the equivalent resistance that would be measured at output terminal with respect to ground. Therefore, the output resistance  $R_{01}$  measured between collector  $C_1$  and ground is equal to that of the collector resistance  $R_C$ . Similarly the output resistance  $R_{02}$  measured at  $C_2$  with respect to ground is equal to that of the collector resistor  $R_C$ .

$$R_{O1} = R_{O2} = R_C$$

(E-5)

The current gain of the differential amplifier is undefined. Like CE amplifier the differential amplifier is a small signal amplifier. It is generally used as a voltage amplifier and not as current or power amplifier.

Q.4. The following specifications are given for the dual input, balanced-output differential amplifier of fig.1.8:

R<sub>C</sub> = 2.2 kΩ, R<sub>B</sub> = 4.7 kΩ, R<sub>in 1</sub> = R<sub>in 2</sub> = 50 Ω, +V<sub>CC</sub> = 10V, -V<sub>EE</sub> = -10 V, β<sub>dc</sub> =100 and V<sub>BE</sub> = 0.715V.

Determine the operating points (I<sub>CQ</sub> and V<sub>CEQ</sub>) of the two transistors.

Figure 1.8 Dual input Balanced output Differential Amplifier

#### Solution:

The value of  $I_{CQ}$  can be obtained from equation (E-1).

$$I_{CQ} = I_{E} = \frac{V_{EE} - V_{BE}}{2R_{E} + \frac{R_{in}}{\beta_{dc}}}$$

$$= \frac{10 - 0.715}{9.4k\Omega + 50/100} = 0.988 \text{mA}$$

The voltage  $V_{CEQ}$  can be obtained from equation (E-2).

The values of  $I_{CQ}$  and  $V_{CEQ}$  are same for both the transistors.

- **Q.5.** The following specifications are given for the dual input, balanced-output differential amplifier:  $RC = 2.2 \ k\Omega$ ,  $RE = 4.7 \ k\Omega$ ,  $Rin \ 1 = Rin \ 2 = 50\Omega$ , +VCC = 10V, -VEE = -10V,  $\beta dc = 100$  and VBE = 0.715V.

- a. Determine the voltage gain.

- b. Determine the input resistance

- *c. Determine the output resistance.*

#### Solution:

(a). The parameters of the amplifiers are same as discussed in example-1 of lecture-1. The operating point of the two transistors are given below

ICQ = 0.988 mA VCEQ=8.54V The ac emitter resistance

$$r_{e}' = \frac{25mV}{I_{e}mA} = \frac{25mV}{0.988mA} = 25.3\Omega$$

Therefore, substituting the known values in voltage gain equation (E-2), we obtain

$$A_{d} = \frac{v_{o}}{v_{id}} = \frac{R_{C}}{r_{e}} = \frac{2.2 \text{ k}\Omega}{25.3} = 86.96$$

b). The input resistance seen from each input source is given by (E-3) and (E-4):

$$R_{i1} = R_{i2} = 2\beta_{ac}r_{e} = (2)(100)(25.3) = 5.06k\Omega$$

(c) The output resistance seen looking back into the circuit from each of the two output terminals is given by (E-5)

$$Ro1 = Ro2 = 2.2 \text{ k} \Omega$$

#### **Q.6.** For the dual input, balanced output differential amplifier of Q.5 above:

- a. Determine the output voltage (vo) if vin 1 = 50mV peak to peak (pp) at 1 kHz and vin 2 = 20 mV pp at 1 kHz.

- **b.** What is the maximum peal to peak output voltage without clipping?

#### Solution:

(a) In Q.5, we have determined the voltage gain of the dual input, balanced output differential amplifier. Substituting this voltage gain (Ad = 86.96) and given values of input voltages in equation, we get

$$v_o = \frac{R_c}{r_e} (v_{in1} - v_{in2}) = 86.96 (50mv - 20mV)$$

= 2.61 Vpp

(b) Note that in case of dual input, balanced output difference amplifier, the output voltage vo is measured across the collector. Therefore, to calculate the maximum peak to peak output voltage, we need to determine the voltage drop across each collector resistor:

Substituting IC = ICQ = 0.988 mA, we get

$$V_{R_{e}} = (2.2k\Omega)(0.988mA) = 2.17 \vee \langle V_{CE} = 8.54 \vee$$

This means that the maximum change in voltage across each collector resistor is  $\pm 2.17$  (ideally) or 4.34 V<sub>PP</sub>. In other words, the maximum peak to peak output voltage with out clipping is (2) (4.34) = 8.68 V<sub>PP</sub>.

**Q.7.** Explain the concept of Inverting & Non – inverting Inputs and Common mode gain for dual input, balanced output difference amplifier

#### Answer:

A dual input, balanced output difference amplifier circuit is shown in fig. 1.9.

Figure 1.9 Dual input Balanced output Differential Amplifier

#### **Inverting & Non – inverting Inputs:**

In differential amplifier the output voltage v<sub>O</sub> is given by

$\begin{array}{l} V_{O} = A_{d} \ (v_{1} - v_{2}) \\ When \quad v_{2} = 0, \ v_{O} = A_{d} \ v_{1} \\ \& \ when \quad v_{1} = 0, \ v_{O} = - \ A_{d} \ v_{2} \end{array}$

Therefore the input voltage  $v_1$  is called the non inventing input because a positive voltage  $v_1$  acting alone produces a positive output voltage  $v_0$ . Similarly, the positive voltage  $v_2$  acting alone produces a negative output voltage hence  $v_2$  is called inverting input. Consequently  $B_1$  is called non-inverting input terminal and  $B_2$  is called inverting input terminal.

#### **Common mode Gain:**

A common mode signal is one that drives both inputs of a differential amplifier equally. The common mode signal is interference, static and other kinds of undesirable pickup etc.

The connecting wires on the input bases act like small antennas. If a differential amplifier is operating in an environment with lot of electromagnetic interference, each base picks up an unwanted interference voltage. If both the transistors were matched in all respects then the balanced output would be theoretically zero. This is the important characteristic of a differential amplifier. It discriminates against common mode input signals. In other words, it refuses to amplify the common mode signals.

The practical effectiveness of rejecting the common signal depends on the degree of matching between the two CE stages forming the differential amplifier. In other words, more closely are the currents in the input transistors, the better is the common mode signal rejection e.g. If  $v_1$  and  $v_2$  are the two input signals, then the output of a practical op-amp cannot be described by simply

$v_0 = A_d (v_1 - v_2)$

In practical differential amplifier, the output depends not only on difference signal but also upon the common mode signal (average).

$$\mathbf{v}_{\mathrm{d}} = (\mathbf{v}_1 - \mathbf{v}_{\mathrm{d}})$$

and  $v_{\rm C} = \frac{1}{2} (v_1 + v_2)$

The output voltage, therefore can be expressed as

$v_0 = A_1 v_1 + A_2 v_2$

Where  $A_1 \& A_2$  are the voltage amplification from input 1(2) to output under the condition that input 2 (1) is grounded.

$$\therefore v_1 = v_C + \frac{1}{2}v_d , \quad v_2 = v_C - \frac{1}{2}v_d$$

Substituting  $\forall_1 \& \forall_2$  in output voltage equation

$$v_0 = A_1 (v_C + \frac{1}{2}v_d) + A_2 (v_C - \frac{1}{2}v_d)$$

$$= \frac{1}{2} (A_1 - A_2) v_d + (A_1 - A_2) v_C$$

$$= A_d v_d + A_C v_C$$

The voltage gain for the difference signal is  $A_d$  and for the common mode signal is  $A_C$ .

The ability of a differential amplifier to reject a common mode signal is expressed by its common mode rejection ratio (CMRR). It is the ratio of differential gain  $A_d$  to the common mode gain  $A_C$ .

$$CMRR = \frac{A_{d}}{A_{c}} = \rho$$

$$\therefore v_{0} = A_{d}V_{d} \left(1 + \frac{1}{\rho}\frac{V_{c}}{V_{d}}\right)$$

Data sheet always specify CMRR in decibels  $CMRR(dB) = 20 \log CMRR$ .

**Q.8.** Derive the expressions for AC analysis of Dual Input, UnBalanced Output Differential Amplifier.

#### Answer:

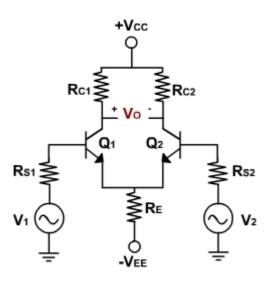

For Dual Input, Unbalanced Output Differential Amplifier, two input signals are given however the output is measured at only one of the two-collector w.r.t. ground as shown in **fig. 1.10**. The output is referred to as an unbalanced output because the collector at which the output voltage is measured is at some finite dc potential with respect to ground..

Figure 1.10 Dual input Unbalanced output Differential Amplifier

#### A.C. Analysis : Differential Voltage Gain Ad

After performing the dc analysis we obtain the operating point of the two transistors.

To find the voltage gain  $A_d$  and the input resistance  $R_i$  of the differential amplifier, the ac equivalent circuit is drawn using r-parameters as shown in **fig. 1.11**. The dc voltages are reduced to zero and the ac equivalent of CE configuration is used.

Figure 1.11 AC equivalent circuit of Dual input Unbalanced output Differential Amplifier

Since the two dc emitter currents are equal. Therefore, resistance  $r'_{e1}$  and  $r'_{e2}$  are also equal and designated by  $r'_{e}$ . This voltage across each collector resistance is shown 180° out of phase with respect to the input voltages  $v_1$  and  $v_2$ . This is same as in CE configuration. The polarity of the output voltage is shown in Figure. The collector  $C_2$  is assumed to be more positive with respect to collector  $C_1$  even though both are negative with respect to to ground.

Applying KVL in two loops 1 & 2.

$$\begin{array}{l} v_1 = R_{S1} \; i_{b1} + i_{e1} \; r'_e \; + (i_{e1} \; + i_{e2} \; ) \; R_E \\ v_2 = R_{S2} \; i_{b2} \; + i_{e2} \; r'_e \; + (i_{e1} \; + i_{e2} \; ) \; R_E \end{array}$$

Substituting current relations,

$$\begin{split} i_{b1} &= \frac{i_{e1}}{\beta}, \ i_{b2} = \frac{i_{e2}}{\beta} \\ V_1 &= \frac{R_{s1}}{\beta} \ i_{e1} + r'_e \ i_{e1} + R_E \ (i_{e1} + i_{e2}) \\ V_2 &= \frac{R_{s2}}{\beta} \ i_{e2} + r'_e \ i_{e2} + R_E \ (i_{e1} + i_{e2}) \end{split}$$

Again, assuming  $R_{S1}$  / b and  $R_{S2}$  / b are very small in comparison with  $R_{\rm E}$  and  $r_e'$  and therefore neglecting these terms,

Solving these two equations,  $i_{e1} \text{ and } i_{e2} \text{ can be calculated.}$

$$i_{e1} = \frac{(r_e + R_E) v_1 - R_E v_2}{(r_e + R_E)^2 - R_E^2}$$

$$i_{e2} = \frac{(r_e + R_E) v_2 - R_E v_1}{(r_e + R_E)^2 - R_E^2}$$

The output voltage  $V_0$  is given by

$V_O = V_{C2}$

- $= -R_{C} i_{C2}$

- $= -R_C i_{e2}$

Substituting  $i_{e2} \mbox{ in the above expression }$

$$V_{o} = -R_{C} \left\{ \frac{(r_{e} + R_{E})V_{2} - R_{E}V_{1}}{(r_{e} + R_{E})^{2} - R_{E}^{2}} \right\}$$

$$V_{o} = R_{C} \left\{ \frac{R_{E}V_{1} - (r_{e} + R_{E})V_{2}}{r_{e}(r_{e} + 2R_{E})} \right\}$$

Since  $R_E \gg r_e$ ,  $(r_e + R_E) \approx R_E$  and  $(r_e + 2R_E) \approx 2R_E$

$$V_o = R_C \frac{R_E (V_1 - V_2)}{2r_e R_E}$$

$$V_o = \frac{R_C}{2r_e} (V_1 - V_2)$$

$$A_{d} = \frac{V_{o}}{(V_{1} - V_{2})} = \frac{R_{C}}{2r_{e}}$$

Thus a differential amplifier amplifies the difference between two input signals. Defining the difference of input signals as  $v_d = v_1 - v_2$  the voltage gain of the dual input balanced output differential amplifier can be given by

$$A_d = \frac{V_c}{V_d} = \frac{R_c}{2r_e}$$

#### Differential Input Resistance: R<sub>i1</sub>andR<sub>i2</sub>

Differential input resistance is defined as the equivalent resistance that would be measured at either input terminal with the other terminal grounded. This means that the input resistance  $R_{i1}$  seen from the input signal source  $v_1$  is determined with the signal source  $v_2$  set at zero. Similarly, the input signal  $v_1$  is set at zero to determine the input resistance  $R_{i2}$  seen from the input signal source  $v_2$ . Resistance  $R_{S1}$  and  $R_{S2}$  are ignored because they are very small.

$$\begin{aligned} \mathsf{R}_{i1} &= \frac{\mathsf{v}_1}{\mathsf{i}_{b1}} \bigg|_{\mathsf{v}_2} = 0 \\ &= \frac{\mathsf{v}_1}{\mathsf{i}_{e1}/\beta} \bigg|_{\mathsf{v}_2} = 0 \end{aligned}$$

Substituting ie1,

$$R_{i1} = \frac{\beta r'_e(r'_e + 2R_E)}{r'_e + R_E}$$

Since  $R_E >> r'_e$

$\therefore r'_e + 2R_E >> 2R_E$

or  $r'_e + R_E >> R_E$

$\therefore R_{i1} = 2\beta r_e'$  (E-3)

Similarly,

$$R_{i2} = \frac{V_2}{i_{b2}} \bigg|_{V_1 = 0}$$

$$= \frac{V_2}{i_{e2} / \beta} \bigg|_{V_1 = 0}$$

$$R_{i2} = 2\beta r'_e \quad (E-4)$$

The factor of 2 arises because the  $r_e'$  of each transistor is in series.

#### Output Resistance: Ro1 and Ro2

Output resistance is defined as the equivalent resistance that would be measured at output terminal with respect to ground. Therefore, the output resistance  $R_0$  measured between collector  $C_2$  and ground is equal to that of the collector resistance  $R_c$ .

$R_0 = R_C$

The current gain of the differential amplifier is undefined. Like CE amplifier the differential amplifier is a small signal amplifier. It is generally used as a voltage amplifier and not as current or power amplifier.

# **Q.9.** Derive the expressions for AC analysis of Dual Input, Balanced Output Differential Amplifier with swamping resistors

#### Answer:

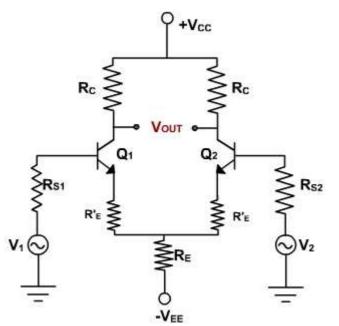

The gain of the differential amplifier is inversely proportional to re which is temperature dependent and hence gain becomes dependent on the temperature. By using external resistors  $R_E$ ' in series with each emitter, the dependence of voltage gain on variations of  $r_e$  can be reduced. It also increases the linearity range of the differential amplifier.**Fig. 1.12**, shows the differential amplifier with swamping resistor  $R_E$ '. The value of  $R_E$ ' is usually large swamp the effect of  $r_e$ .

**Figure 1.12** Dual input Balanced output Differential Amplifier with Swamping Resistor

#### **DC Analysis:**

To obtain the operating point ( $I_{CC}$  and  $V_{CEQ}$ ) for differential amplifier dc equivalent circuit is drawn by reducing the input voltages  $v_1$  and  $v_2$  to zero as shown in **fig. 1.13**.

The internal resistances of the input signals are denoted by  $R_S$  because  $R_{S1} = R_{S2}$ . Since both emitter biased sections of the different amplifier are symmetrical in all respects, therefore, the operating point for only one section need to be determined. The same values of  $I_{CQ}$  and  $V_{CEQ}$  can be used for second transistor  $Q_2$ .

In DC equivalent circuit there is addition of  $R_{E}'$  in emitter path of both the transisitors, therefore the  $I_{C}$  and  $V_{CE}$  equations will have the term  $R_{E}$  repacted by  $R_{E} + R_{E}'$ .

Figure 1.13 DC equivalent circuit of Dual input Balanced output Differential Amplifier with Swamping Resistor

$$I_E = I_C = \frac{V_{EE} - V_{BE}}{2R_E + R_E'}$$

$$V_{CE} = V_{CC} + V_{BE} - I_C R_C$$

AC analysis:

To find the voltage gain  $A_d$  and the input resistance  $R_i$  of the differential amplifier, the ac equivalent circuit is drawn using r-parameters as shown in **fig. 1.14**. The dc voltages are reduced to zero and the ac equivalent of CE configuration is used.

In the AC equivalent circuit the ac emitter resistance  $r_e$  is in series with swamping resistor  $R_E$ ', therefore the equations will be changed with  $r_e$  replaced by  $r_e+R_E$ '.

Figure 1.14 AC equivalent circuit of Dual input Balanced output Differential Amplifier with Swamping Resistor

Differential gain A<sub>d</sub>

$$A_{d} = \frac{V_{o}}{(V_{1} - V_{2})} = \frac{R_{C}}{r_{e} + R_{E}'}$$

Input resistance R<sub>i1</sub> and R<sub>i2</sub>

$$R_{i1} = R_{i2} = 2\beta \left( r_e + R_E' \right)$$

Output resistance  $R_{o1}$  and  $R_{o2}$

$$R_{o1} = R_{o2} = R_C$$

- **Q.10.** The following specifications are given for the dual input, balanced-output differential amplifier with swamping resistor:  $R_C = 2.2 \ k\Omega$ ,  $R_E = 4.7 \ k\Omega$ ,  $R_E' = 100\Omega$ ,  $R_{in1} = R_{in2} = 50\Omega$ ,  $+V_{CC} = 10V$ ,  $-V_{EE} = -10 \ V$ ,  $\beta_{dc} = 100 \ and \ V_{BE} = 0.715 \ V$ .

- a. Determine the voltage gain.

- b. Determine the input resistance

- c. Determine the output resistance.

#### Solution:

The operating point of the transistors is given by

$$I_E = I_C = \frac{V_{EE} - V_{BE}}{2R_E + R_E'}$$

$$I_C = \frac{10 - 0.715}{2 \times 4.7 \text{ k}\Omega + 100} = 0.977 \text{mA}$$

$$V_{CE} = V_{CC} + V_{BE} - I_C R_C$$

$$V_{CE} = 10 + 0.715 - 0.977 \text{mA} \times 2.2 \text{ k}\Omega = 8.565 \text{V}$$

The ac emitter resistance re is given by

$$r_e = \frac{V_T}{I_E} = \frac{25mV}{0.977mA} = 25.588\Omega$$

The voltage gain is given by

$$A_d = \frac{R_C}{r_e + R_E} = \frac{2.2 \text{ k}\Omega}{25.888 + 100} = 17.476$$

Input resistance  $R_{\mathrm{i}1}$  and  $R_{\mathrm{i}2}$

$$R_{i1} = R_{i2} = 2\beta (r_e + R_E) = 2 \times 100 \times (25.888 + 100) = 25.176 \text{k}\Omega$$

Output resistance  $R_{\rm o1}$  and  $R_{\rm o2}$

$$R_{o1} = R_{o2} = R_C = 2.2 \text{ k}\Omega$$

# UNIT No 2

## Operational amplifier fundamentals

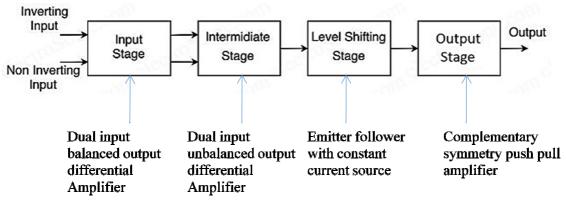

**Q1.** *Draw the block diagram of operational amplifier and working of each block in brief. Comment on the parameters contributed by each stage.*

Answer:

#### Figure 2.1: Block diagram of Operational amplifier

OPAMP is basically a differential amp i.e., it will amplify dc as well as ac i/p signals and was originally designed for computing such mathematical functions as addition, subtraction, multiplication and integration. Thus the name operational amplifier stems from its original use for these mathematical operation and is abbreviated to opamp. Since opamp is a multistage amplifier it can be represented by the block diagram as shown in above figure.

**Input stage:** The input stage is a dual input, balanced output differential amplifier. The two inputs are inverting and non- inverting i/p terminals. This stage provides most of the voltage gain of the OP-AMP and also establishes the value of i/p resistance Ri.

**Intermediate stage:** This is usually another differential amp. The i/p stage drives the stage. The stage is a dual –i/p unbalanced o/p differentiated amp. Due to direct coupling dc voltage at the output of intermediate stage is well above the ground potential.

**Level- shifting stage:** Due to direct coupling used between the 1st 2 stages, the i/p of level shifting stage is an amplified signal with some non – zero dc level. Level shifting stage is used to bring dc level to zero volts with respect to gnd.

**Output stage:** This stage is normally a push pull complementary o/p stage. It increases the magnitude of voltage swing and raises the current supplying capability of OP-AMP. It also ensures that the o/p resistance of OPAMP is low.

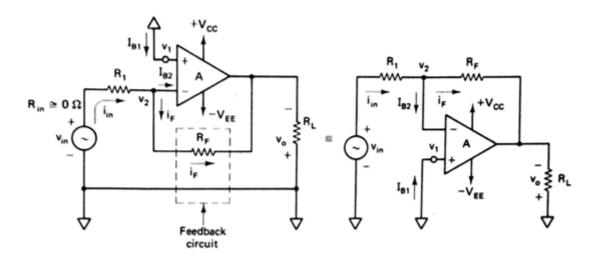

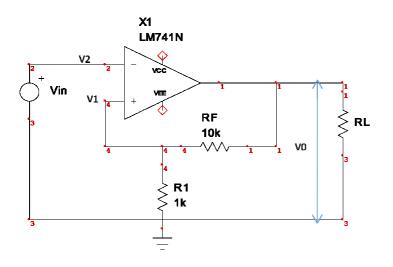

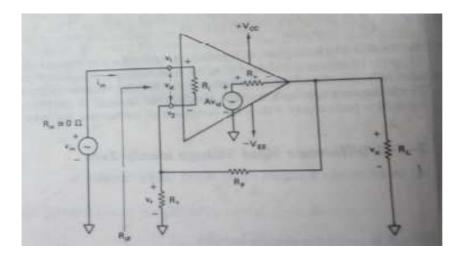

**Q2.** Draw the circuit of voltage shunt feedback amplifier using opamp and derive the expression for closed loop gain, input resistance with feedback, output resistance with feedback and banwidth with feedback.

Answer:

Figure 2.2: Voltage shunt feedback amplifier using opamp

Figure 2 shows the voltage shunt feedback amplifier using op-amp. The input voltage drives the inverting terminal, and the amplified as well as inverted output signal is also applied to the inverting input via feedback resistor RF. This arrangement forms a negative feedback because any increase in the output signal results in a feedback signal into the inverting input, causing a decrease in the output signal.

The noninverting terminal is grounded, and the feedback circuit has only one resistor RF. However, an extra resistor R1 is connected in series with the input signal. The different closed loop parameters for inverting op-amp are:

- 1. Voltage gain

- 2. Input and output resistances

- 3. Bandwidth

- 4. Total output offset voltage.

#### **Voltage Gain :**

Apply KCL at the input node V2,

Iin  $=I_F+I_B$

Since input impedance is very large IB = 0,

$\text{Iin}\approx I_{\text{F}}$

$$V_{IN} - V_2 R_1 = V_2 - V_0 R_F$$

For non saturated output we can write,

V<sub>O</sub>=AV<sub>id</sub>

$$A = \frac{V_O}{V_{id}}$$

Open loop gain of op-amp is large Vid = 0,

$V_1 = V_2$

$V_1 = 0$ ,  $V_2$  is also virtually at zero potential. i.e  $V_2 = 0$ ,

$$\frac{V_{in}}{R_1} = \frac{V_o}{R_F}$$

$$\frac{V_o}{V_{in}} = -\frac{R_F}{R_1} = A_F$$

#### **Input Resistance :**

The input resistance is found using millerizing the feedback resistor RF, that is, split RF into two miller component as shown in Figure 2.

Figure 2.3: Inverting amplifier wih millerised feedback resistor

The input resistance with feedback  $R_F = R_1 + \frac{R_F}{1+A} \parallel R_i$ Since Ri and A are very large,  $R_1 + \frac{R_F}{1+A} \parallel R_i = 0$ Hence,  $R_{iF}=R_1$

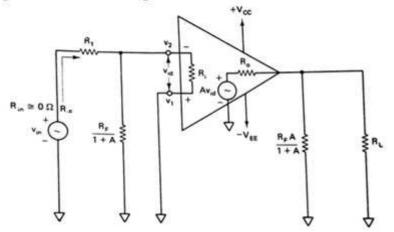

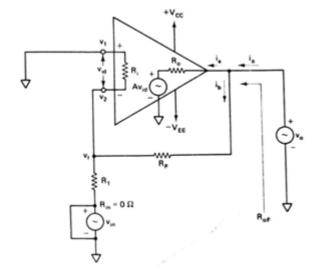

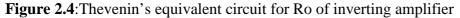

#### **Output Resistance :**

The output resistance with feedback RoFRoF is the resistance measured at the output terminal of the feedback amplifier. The output resistance of the noninverting amplifier was obtained by using Thevenin's theorem. Thevenin's equivalent circuit for RoFRoF of the inverting amplifier is shown in Figure 3. The RoFRoF of the inverting amplifier is identical because the output

connections in both amplifiers are the same.

$$R_{OF} = \frac{R_0}{1 + A\beta}$$

Where,

Ro= output resistance of the op-amp A= open loop voltage gain of the op-amp

B= gain of the feedback circuit.

#### **Bandwidth with Feedback :**

The gain-bandwidth product of a single break frequency op-amp is always constant. The gain of the amplifier with feedback is always less than the gain without feedback. Therefore, the bandwidth of the amplifier with feedback fFfF must be larger than that without feedback.

$$f_F = f_0(1 + A\beta)$$

where

fo = break frequency of the op-amp= unity gain bandwidth / open loop voltage gain

#### **Total Output Offset Voltage with Feedb0ack :**

When temperature and power supply voltages are fixed, the output offset voltage is a function of the gain of an op-amp. The output offset voltage with feedback VooTVooT must always be smaller than that without feedback. Specially,

Total output offset voltage with feedback = total output offset voltage without feedback / 1+AB That is,

$$V_{OOT} = \pm \frac{V_{sat}}{1 + A\beta}$$

Where

$\pm$ Vsat = saturation voltages A = open-loop voltage gain of the op-amp

B = Gain of the feedback circuit

$B = R_1 / R_1 + R_F$

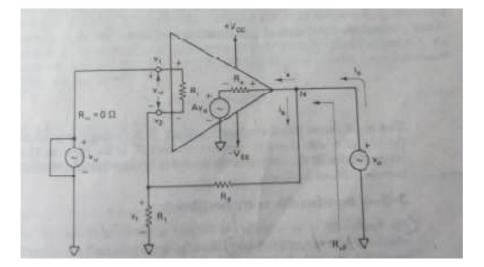

**Q3.** Draw the circuit of voltage series feedback amplifier using opamp and derive the expression for closed loop gain, input resistance with feedback, output resistance with feedback and bandwidth with feedback.

#### Answer:

In a negative feedback amplifier, a small portion of the output voltage is fed back to the input. When the feedback voltage is applied in series with the signal voltage, the arrangement is Voltage Series Negative Feedback Amplifier.

Figure 2.5: voltage series feedback amplifier using opamp

the amplifier has a voltage gain  $(A_v)$ , and its output voltage  $(v_o)$  is applied to a feedback network that reduces  $v_o$  by a factor (B) to produce a feedback voltage  $(v_f)$ . The feedback network may be as simple as the resistive voltage divider shown in Fig.

#### **Negative feedback:**

referring to the figure of voltage series feedback amplifier, Kirchoff's voltage equation for input loop is

$$V_{id} = V_{in} - V_f$$

where Vinis input voltage

$V_f$  is feedback voltage

$V_{id}$  is difference inputs voltage

From the above equation difference voltage is equal to the input voltage V<sub>in</sub> minus feedback

voltage  $V_f$ . In other word feedback voltage always opposes the input voltage(or it is out of phase by 180 with respect to input voltage), hence f eedback is said to be negative.

#### **Close loop Voltage gain :**

$$Af = \frac{V0}{Vin}$$

$$V0 = A(V1 - V2)$$

referring to figure

$$V1 = Vin$$

$V2 = Vf = \frac{R1V0}{R1 + Rf}$

Therefore

$$V0 = A(Vin - \frac{R1Vo}{R1 + Rf})$$

Rearraging we get  $Vo = \frac{A(R1+Rf)Vin}{R1+Rf+AR1}$

Thus  $Af = \frac{Vo}{Vin} = \frac{A(R1+Rf)}{R1+Rf+AR1}$

generally A is very  $large(10^5)$  therefore

$AR1 \gg (R1 + Rf)$  and  $R1 + Rf + AR1 \approx AR1$  $Af = \frac{Vo}{Vin} = 1 + \frac{Rf}{R1}$

Gain of the feedback circuit  $\beta$  is the rat of Vf and V0

$$\beta = \frac{Vf}{V0} = \frac{R1}{R1 + Rf}$$

therefore we conclude that

$$Af = \frac{1}{\beta}$$

Block diagram representation of non inverting amplifier with feedback

close loop voltage gain Af can be expressed in terms of open loop gain and feedback ciruit gain as follows

$$Af = \frac{A(\frac{R1+Rf}{R1+Rf})}{\frac{R1+Rf}{R1+Rf} + \frac{AR1}{R1+Rf}}$$

$$Af = \frac{A}{1+A\beta}$$

Af= Closed loop gain

A= open loop gain

$\beta$ = gain of the feedback circuit

A  $\beta$ = loop gain

### **Difference Input voltage Ideally zero:**

$$Vid = \frac{V0}{A}$$

Since A is very large (ideally infinite)

$$V_{id} \cong 0 \tag{1}$$

therefore  $V_1 = V_2$

From the figure  $V_1 = V_{in}$

$$V_2 = V_f$$

$$= \frac{R_1 V_o}{R_1 + R_f}$$

(2)

Substituting values of  $V_1$  and  $V_2$  in equation (2)

$$V_{in} = \frac{R_1 V_o}{R_1 + R_f}$$

that is

$$A_F = \frac{V_0}{V_{in}} = 1 + \frac{R_F}{R_1}$$

Input Resistance with Feedback:

Figure 2.6:input resistance of with feedback

Figure shows voltage series feedback amplifier with the opamp equivalent circuit. In this circuit  $R_i$  is the input resistance of the opamp, and  $R_{iF}$  is the input resistance of the amplifier with feedback. The input resistance with feedback is defined as

$$R_{iF} = \frac{V_{in}}{I_{in}}$$

$$R_{iF} = \frac{V_{in}}{\frac{V_{id}}{R_i}}$$

However  $V_{id} = \frac{V_0}{A}$ And  $V_o = \frac{A}{1+A\beta}V_{in}$

Therefore  $R_{iF} = R_i \frac{V_{in}}{\frac{V_0}{A}}$

$$= AR_i \frac{V_{in}}{\frac{AV_{in}}{(1+A\beta)}}$$

$$= R_i (1+A\beta)$$

This means that input resistance of the opamp with feedback is  $(1 + A\beta)$  times without feedback.

## **Output resistance with Feedback:**

Output resistance is the resistance determine looking back into the feedback amplifier from output terminal as shown in figure. This resistance can be obtained by Thevenin's theorem for dependent source. To find output resistance with feedback  $R_{oF}$ , reduce independent source  $V_{in}$  to zero, apply an external voltage  $V_o$ , and then calculate the resulting current  $i_o$ .

Figure 2.7: Output resistance of with feedback

In short  $R_{oF}$  is defined as follows:

$R_{oF} = \frac{v_o}{i_o}$

Writing Kirchoff's current equation at output node N, we get

$$i_o = i_a + i_b$$

Since  $[(R_F + R_1) \parallel R_i] \gg R_0$  and  $i_a \gg i_b$  therefore,

$$i_o \cong i_a$$

The current  $i_o$  can be found by writing Kirchoff's voltage equation for the output loop

$$v_o - R_o i_o - AV_{id} = 0$$

$$i_o = \frac{v_o - AV_{id}}{R_o}$$

However  $V_{id} = V_1 - V_2$

$$= 0 - V_f$$

$$= -\frac{R_1 v_o}{R_1 + R_f} = -\beta v_o$$

Therefore  $i_o = \frac{v_o + A\beta v_o}{R_0}$

Substituting values of io in equation 3, we get

$$R_{oF} = \frac{v_o}{\frac{v_o + A\beta v_o}{R_o}}$$

$$R_{oF} = \frac{R_o}{1 + A\beta}$$

This result shows that output resistance of voltage series feedback amplifier is  $1/(1+A\beta)$  times output resistance  $R_o$  of the opamp.

## Bandwidth with feedback:

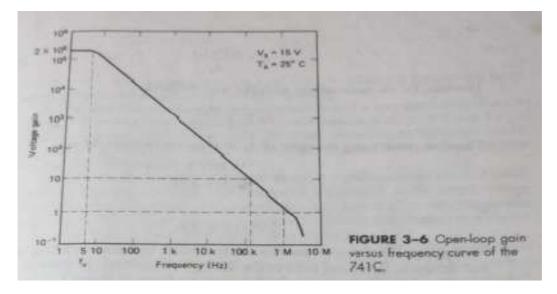

The bandwidth of an amplifier is defined as the band of frequencies for which the gain remains constant. Manufacturer generally specify either the gain bandwidth product or supply open loop gain versus frequency curve for the opamp as shown in figure below..For 741 opamp , 5hz is the break ,the frequency at which the gain A is 3 dB down from its value at 0 Hz.

Figure 2.8:Open loop gain versus frequency curve of the 741C

This is denoted by  $f_o$ . On the other hand the frequency at which gain equals to 1 is known as unity gain bandwidth (UGB). The relationship between break frequency  $f_o$ , open loop gain A,bandwidth with feedback  $f_F$  and closed loop gain  $A_F$  can be established as follows.

$$UGB = (A)(f_0)$$

Where A= Open loop voltage gain

f<sub>o</sub>=Break frequency of opamp

or only for a single break frequency opamp

$$UGB = (A_F)(F_F)$$

Where  $A_F$  is the close loop gain

$F_F$  is bandwidth with feedback

Therefore

$$(A)(f_{o}) = (A_{F})(F_{F})$$

$$f_{F} = \frac{(A)(f_{o})}{A_{F}}$$

(4)

For the non inverting amplifier with feedback

$$A_F = \frac{A}{1 + A\beta}$$

Therefore substituting values in equation (4), we get

$$f_F = \frac{(A)(f_0)}{\frac{A}{1+A\beta}}$$

$$f_F = f_0(1 + A\beta)$$

This shows that bandwidth of non inverting amplifier with feedback  $f_F$  is equal to its bandwidth without feedback  $f_0$  times  $(1 + A\beta)$ .

## Total output offset voltage with Feedback:

Total output offset voltage with feedback =  $\frac{\text{Total output offset voltage without feedback}}{1 + A\beta}$

$$V_{ooT} = \frac{\pm V_{sat}}{1 + A\beta}$$

Where 1/1+A $\beta$  is less than 1 and  $\pm$  V<sub>sat</sub> is saturation voltages, maximum voltages the output of

an opamp can reach.

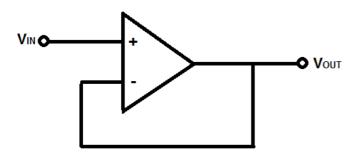

**Q** 4. Draw the circuit of voltage follower using opamp and derive the expression for closed loop gain , input resistance with feedback, output resistance with feedback and banwidth with feedback.

Answer:

Figure 2.9 : Voltage follower

When noninverting l is configured for unity gain, it is called voltage follower because output voltage is equal to input and in phase with input. The Voltage Follower, also called a buffer does not amplify or invert the input signal but instead provides isolation between two circuits. The input impedance is very high while the output impedance is low avoiding any loading effects within the circuit. As the output is connected back directly to one of the inputs, the overall gain of the buffer is 1.

$$Af = 1$$

$$Rif = ARi$$

$$Rof = \frac{R_0}{A}$$

$$f_F = Af_0$$

$$V_{00T} = \frac{\pm V_{SAT}}{A}$$

**Q 5.** For the non-inverting amplifier using opamp  $R_1=1$  K $\Omega$ ,  $R_f=10$ K $\Omega$  and the opamp used has  $A=2*10^5$ ,  $R_i=2M \Omega$ ,  $R_o=75\Omega$ , UGB=1MHz,  $\pm V_{sat}=\pm 13v$ . Determine closed loop gain, input and output resistance with feedback, bandwidth with feedback and total output offset voltage with feedback.

## Answer:

$$\beta = \frac{R1}{R1+Rf} = \frac{1k}{1k+10k} = \frac{1}{11}$$

$$1 + A\beta = 1 + 20000 \times \frac{1}{11} = 18182.8$$

$$A_F = \frac{A}{1+A\beta} = \frac{200000}{18182.8} = 10.99$$

$$R_{iF} = R_i(1 + A\beta) = 2M(1 + 18182.8) = 36.4G\Omega$$

$$R_{oF} = \frac{75}{18.182.8} = 4.12m\Omega$$

$$f_F = 5 \times 18182.8 = 90.9 \ kHz$$

$$V_{ooT} = \frac{\pm 13}{18182.8} = \pm 0.715 \ mV$$

**Q 6.** For the inverting amplifier using opamp  $R_1 = 470\Omega$ ,  $R_f = 4.7K\Omega$  and the opamp used has  $A = 2*10^5$ ,  $R_i = 2M \Omega$ ,  $R_o = 75\Omega$ , UGB = 1MHz,  $\pm V_{sat} = \pm 13v$ . Determine closed loop gain, input and output resistance with feedback, bandwidth with feedback and total output offset voltage

with feedback.

Answer:

$$k = \frac{R_f}{R_1 + R_f} = \frac{4700}{470 + 4700} = \frac{1}{1.1}$$

$$\beta = \frac{R_1}{R_1 + R_f} = \frac{470}{470 + 4700} = \frac{1}{11}$$

$$1 + A\beta = 1 + 20000 \times \frac{1}{11} = 18182.8$$

$$A_F = -\frac{R_f}{R_1} = \frac{4700}{470} = -10$$

$$R_{iF} = R_1 + \frac{R_f}{1+A} \parallel R_i = 470 + \frac{4700}{1+20000} \parallel 2M = 470\Omega$$

$$R_{oF} = \frac{R_o}{1+A\beta} = \frac{75}{18.182.8} = 4.12m\Omega$$

$$f_F = \frac{5 \times 18182.8}{\frac{1}{1.1}} = 100 \text{ kHz}$$

$$V_{ooT} = \frac{\pm V_{SAT}}{1+A\beta} = \frac{\pm 13}{18182.8} = \pm 0.715 \text{ mV}$$

**Q.7** For the voltage follower using opamp  $R_1=1$  K $\Omega$ ,  $R_f=10$ K $\Omega$  and the opamp used has  $A=2*10^5$ ,  $R_i=2M \Omega$ ,  $R_o=75\Omega$ , UGB=1MHz,  $\pm V_{sat}=\pm 13v$ . Determine closed loop gain, input and output resistance with feedback, bandwidth with feedback and total output offset voltage with feedback.

### Answer:

$$Af = 1$$

$$R_{if} = ARi = 20000 \times 2M = 400G\Omega$$

$$Rof = \frac{R_0}{A} = \frac{75}{20000} = 0.375m\Omega$$

$$f_F = Af_0 = 20000 \times 5 = 1MHz$$

$$V_{00T} = \frac{\pm V_{SAT}}{A} = \frac{\pm 13}{20000} = \pm 65\mu V$$

**Q** 8. For the inverting amplifier R1 = 4.7 k and Rf = 470k. Determine maximum possible output offset voltage due to i) The input offset voltage Vio ii) The input bias current IB iii) What value of ROM is needed to reduce the effect of input bias current IB? Use opamp 741 type.

## Answer:

Inverting Amplifier with  $R_1$ = 4.7 k and  $R_f$ = 470k,  $I_{io}$ =200nA,  $I_B$ = 500nA

$Vo_{lio} = R_f I_{io} = 470k \times 200nA = 94mV$

$Vo_{IB} = R_f I_B = 470k \times 500nA = 235mV$

$R_{oM} = R_1 \parallel R_f = 4.7k \parallel 470k = 4.653k\Omega$

**Q. 9.** The op-amp used as non inverting amplifier with  $R_1 = 47 \ k\Omega \ R_F = 470 \ k\Omega$  The opamp has input offset voltage of 10 mv. Calculate the maximum output offset voltage caused by  $V_{IO}$ . Also design the compensation network for  $V_{IO}$ .

Answer: Noninverting Amplifier with  $R_1 = 47 \text{ k}\Omega$ ,  $R_F = 470 \text{ k}\Omega$ ,  $V_{IO} = 10 \text{mv}$ .

Figure 2.10 : non inverting amplifier with Compensation

$$V_{oo} = (1 + \frac{R_f}{R_1}) V_{IO}$$

$$= \left(1 + \frac{470k}{47k}\right) 10mv = 0.11v$$

Compensation network

$$V_{IO} = \frac{R_c}{R_b} \times V_{max}$$

$$V_{max} = \pm V_{cc} = \pm 15\nu$$

Let R<sub>c</sub>= 10Ω

$$R_b = R_c \frac{V_{max}}{V_{IO}}$$

$$= 10 \times \frac{15}{10m} = 15k\Omega$$

$$R_b \gg \frac{R_a}{4}$$

$$R_b = 10 \times \frac{R_a}{4}$$

$R_a = 6K\Omega$

Therefore  $R_a = 6K\Omega$ ,  $R_b = 15K\Omega$  $R_c = 10\Omega$

**Q.10.The** *OP*-amp used as inverting amplifier has following specification  $\Delta V_{io} \Delta T = 25 u V/^{\circ}C$ ,  $\Delta I_{io} \Delta T = 15 n A/^{\circ}C$ . The amplifier uses  $R_1 = 100\Omega$  and  $R_f = 8.2k\Omega$ ,  $+V_{ss} = \pm 15v$  and is nulled at 25°C. A sine wave of l0mv peak amplitude at 100 Hz is applied as input to the circuit. Draw the output voltage waveform at 25°C and 45°C.

Answer: inverting amplifier  $\Delta V_{io}/\Delta T=25 uV/^{\circ}C$ ,  $\Delta I_{io}/\Delta T=15$  nA/°C,  $R_{1}=100\Omega$  and  $R_{f}=8.2k\Omega,$  +V $_{ss}=\pm$ 15v

$\Delta T = 45 - 25 = 20$

$$\Delta V_{ooT_{45}} = \left(1 + \frac{R_f}{R_1}\right) \left(\frac{\Delta V_{IO}}{\Delta T}\right) \times \Delta T + R_f \left(\frac{\Delta I_{IO}}{\Delta T}\right) \times \Delta T$$

$$= \left(1 + \frac{8.2k}{100}\right) (25uv) \times 20 + 8.2k \times (15nA) \times 20$$

$$= 0.0415 + 0.00246$$

$$= 43.95mv$$

$$Vo_{25} = -\frac{R_f}{R_1} \times Vin_p$$

$$= -\frac{8.2k}{100} \times 10mv$$

= -0.8v

$Vo_{45} = -0.8 v \pm 43.95 mv$

$= -.84395v \ or - 0.75065v$

## Unit-3

## Linear Applications of Operational Amplifier

**Q.1.** Draw the circuit of Inverting summer amplifier and derive the expression for output voltage.

## Answer:

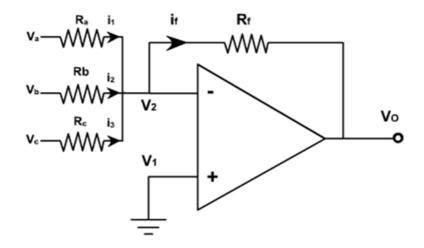

The configuration is shown in figure. With three input voltages va, vb & vc. Depending upon the value of Rf and the input resistors Ra, Rb, Rc the circuit can be used as a summing amplifier, scaling amplifier, or averaging amplifier.

Figure 3.1 Inverting Summing Amplifier

Again, for an ideal OPAMP,  $V_1 = V_2$ . The current drawn by OPAMP is zero. Thus, applying KCL at  $V_2$  node

$$i_1 + i_2 + i_3 = i_f$$

$$\frac{V_a}{R_a} + \frac{V_b}{R_b} + \frac{V_c}{R_c} = -\frac{V_o}{R_f}$$

$$V_o = -\left(\frac{R_f}{R_a}V_a + \frac{R_f}{R_b}V_b + \frac{R_f}{R_c}V_c\right)$$

If in the circuit shown  $R_a = R_b = R_c = R$

$$V_o = -\frac{R_f}{R}(V_a + V_b + V_c)$$

This means that the output voltage is equal to the negative sum of all the inputs times the gain of the circuit  $R_{f}/R$ ; hence the circuit is called a summing amplifier. When  $R_{f}=R$  then the output voltage is equal to the negative sum of all inputs.

$$V_o = -(V_a + V_b + V_c)$$

If each input voltage is amplified by a different factor in other words weighted differently at the output, the circuit is called then scaling amplifier.

$$\frac{R_f}{R_a} \neq \frac{R_f}{R_b} \neq \frac{R_f}{R_c}$$

$$V_o = -\left(\frac{R_f}{R_a}V_a + \frac{R_f}{R_b}V_b + \frac{R_f}{R_c}V_c\right)$$

The circuit can be used as an averaging circuit, in which the output voltage is equal to the average of all the input voltages.

In this case,  $R_a = R_b = R_c = R$  and  $R_f / R = 1 / n$  where n is the number of inputs. Here  $R_f / R = 1 / 3$ .

$$V_o = -\frac{(V_a + V_b + V_c)}{3}$$

In all these applications input could be either ac or dc.

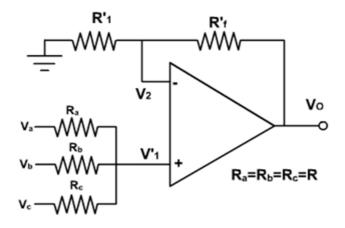

**Q.2.** Draw the circuit of Non-Inverting summer amplifier and derive the expression for output voltage.

If the input voltages are connected to non-inverting input through resistors, then the circuit can be used as a summing or averaging amplifier through proper selection of  $R_a$ ,  $R_b$ ,  $R_c$  and  $R_f$ . as shown in fig. 3.

Figure 3. 2 Non-Inverting Summing Amplifier

To find the output voltage expression,  $V_1$  is required. Applying superposition theorem, the voltage  $V_1$  at the non-inverting terminal is given by

$$V_1 = \left( \left( \frac{R_b \| R_c}{R_a} \right) V_a + \left( \frac{R_a \| R_c}{R_b} \right) V_b + \left( \frac{R_a \| R_b}{R_c} \right) V_c \right)$$

For  $R_a = R_b = R_c = R$

$$V_{1} = \left( \left( \frac{R_{2}}{R + R_{2}} \right) V_{a} + \left( \frac{R_{2}}{R + R_{2}} \right) V_{b} + \left( \frac{R_{2}}{R + R_{2}} \right) V_{c} \right)$$

$$V_1 = \frac{(V_a + V_b + V_c)}{3}$$

Hence the output voltage is

$$V_{o} = \left(1 + \frac{R_{f}}{R_{1}}\right)V_{1} = \left(1 + \frac{R_{f}}{R_{1}}\right)\left(\frac{(V_{a} + V_{b} + V_{c})}{3}\right)$$

This shows that the output is equal to the average of all input voltages times the gain of the circuit (1+ Rf / R1), hence the name averaging amplifier.

If (1+Rf/R1) is made equal to 3 then the output voltage becomes sum of all three input voltages.

$V_o = V_a + V_b + V_c$

Hence, the circuit works as non-inverting summing amplifier.

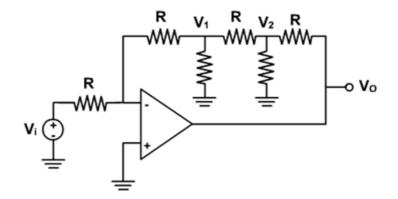

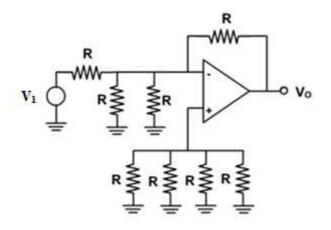

**Q.3.** Determine the gain  $V_O / V_i$  of the circuit of figure 3.3

Figure 3. 3 Circuit for Q.3.

## Solution:

Applying KCL at inverting node of OP-AMP

$$\frac{V_i - 0}{R} = \frac{0 - V_1}{R}$$

$$\frac{V_i}{R} = \frac{-V_1}{R}$$

$$V_1 = -V_i$$

Applying KCL to node V<sub>1</sub>,

$$\frac{0 - V_1}{R} = \frac{V_1}{R} + \frac{V_1 - V_2}{R}$$

$$\frac{V_2}{R} = \frac{-3V_1}{R}$$

$$V_2 = -3V_1 = -3V_i$$

Applying KCL to node V<sub>2</sub>,

$$\frac{V_1 - V_2}{R} = \frac{V_2}{R} + \frac{V_2 - V_0}{R}$$

$$\frac{V_o}{R} = \frac{3V_2}{R} - \frac{V_1}{R}$$

$$\frac{V_o}{R} = \frac{9V_i}{R} - \frac{V_i}{R}$$

$$V_o = -8V_i$$

$$\frac{V_o}{V_i} = -8$$

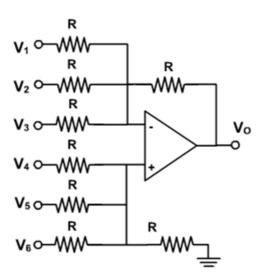

**Q.4.** Find the relationship between  $V_0$  and  $V_1$  through  $V_6$  in the circuit of *figure 3.4*

Figure 3. 4 Circuit for Q.4

## Solution:

Let's consider of V1 (singly) by shorting the others i.e. the circuit then looks like as shown in **fig. 3.5.**

Figure 3. 5 Circuit with superposition theorem-1

The circuit behaves as simple inverting amplifier and  $V_{\rm ol}$  is given by

$$V_{o1} = -\frac{R}{R}V_1 = -V_1$$

The circuit considering  $V_2$  and  $V_3$  is also same and output  $V_{\rm o2}$  and  $V_{\rm o3}$  is given by

$$V_{o2} = -\frac{R}{R}V_2 = -V_2$$

and  $V_{o3} = -\frac{R}{R}V_3 = -V_3$

Let as now consider the case of  $V_4$  with other inputs shorted, circuit looks like as shown in **figure 3.6**

$V_4$

Figure 3. 6 Circuit with superposition theorem-2

The non-inverting potential is now given by

$$V_{N4} = \frac{R_{3}}{R + R_{3}} V_{4}$$

The output voltage  $Vo_4$  due to  $V_4$  if of non-inverting given by

$$V_{o4} = \left(1 + \frac{R}{R/3}\right) V_{N4}$$

$$V_{o4} = \left(1 + \frac{R}{R/3}\right) \times \frac{R/3}{R + R/3} V_4$$

$$V_{o4} = V_4$$

The circuit considering  $V_5$  and  $V_6$  is also same and output  $V_{\rm o5}\,\text{and}\,V_{\rm o6}$  is given by

$$V_{o5} = V_5 \qquad \text{and} \qquad V_{o6} = V_6$$

The total output voltage is given by

$$V_o = V_{01} + V_{02} + V_{03} + V_{04} + V_{05} + V_{06}$$

$$V_o = -V_1 - V_2 - V_3 + V_4 + V_5 + V_6$$

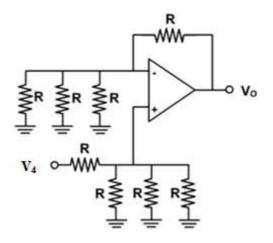

**Q.5.** Show that the circuit of **figure 3.7** has  $A = V_0 / V_i = -K(R_2 / R_1)$  with  $K = 1 + R_4 / R_2 + R_4 / R_3$ , and  $R_i = R_1$ . Also specify resistance not larger than 100 K to achieve A = -200 V / V and  $R_i = 100$  K.

Figure 3.7 Circuit for Q.5

Solution:

Applying KCL at inverting node,

$$\frac{V_i - V_1}{R_1} = \frac{V_1 - V_2}{R_2}$$

$$\frac{V_i}{R_1} = \frac{-V_2}{R_2}$$

$$V_2 = -V_i \frac{R_2}{R_1}$$

Applying KCL at feedback node  $V_2$ ,

$$\begin{split} \frac{V_1 - V_2}{R_2} &= \frac{V_2 - V_0}{R_4} + \frac{V_2}{R_3} \\ &= \frac{-V_2}{R_2} = \frac{V_2 - V_0}{R_4} + \frac{V_2}{R_3} \\ &= \frac{-V_i \frac{R_2}{R_1} - V_0}{R_4} + \frac{-V_i \frac{R_2}{R_1}}{R_3} \\ &= \frac{-V_i R_2 - V_0 R_1}{R_1 R_4} + \frac{-V_i R_2}{R_1 R_3} \\ &= \frac{-V_i R_2 R_3 - V_0 R_1 R_3 - V_i R_2 R_4}{V_i (R_3 R_4 + R_2 R_3 + R_2 R_4) = -V_0 R_1 R_3} \\ &= -\left(\frac{R_3 R_4 + R_2 R_3 + R_2 R_3 + R_2 R_4}{R_1 R_3}\right) \\ &= \frac{V_0}{V_i} = -\frac{R_2}{R_1} \left(\frac{R_4}{R_2} + \frac{R_4}{R_3} + 1\right) \\ &= \frac{V_0}{V_i} = -\frac{R_2}{R_1} \left(1 + R_4 \left(\frac{R_2 + R_3}{R_2 R_3}\right)\right) \\ &= \frac{V_0}{V_i} = -k \frac{R_2}{R_1} \end{split}$$

where

$$k = \left(1 + R_4 \left(\frac{R_2 + R_3}{R_2 R_3}\right)\right)$$

The circuit is inverting configuration therefore  $R_i = R_1 = 100 K\Omega$

Given  $R_i=100K$  and  $R_1=R_2=R_4=100K$

$$\left|\frac{V_o}{V_i}\right| = \frac{R_2}{R_1} \left(1 + R_4 \left(\frac{R_2 + R_3}{R_2 R_3}\right)\right) = 200$$

$$1 + 100K \left(\frac{100K + R_3}{100KR_3}\right) = 200$$

$R_3 = 505\Omega$

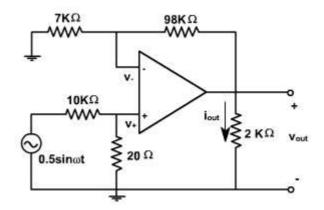

**Q.6.** Find  $V_{out}$  and  $i_{out}$  for the circuit shown in figure 3.8. The input voltage is sinusoidal with amplitude of 0.5 V.

Figure 3.8 Circuit for Q.6

## Solution:

We begin by writing the KCL equations at both the + and – terminals of the op-amp.

Apply KVL at the inverting terminal,

$$\frac{V_- - V_{out}}{9.8 \times 10^4} + \frac{V_- - 0}{7000} = 0$$

Therefore,

$$15V_{-} = V_{out}$$

For the positive terminal,

$$\frac{V_+ - V_{in}}{10^4} + \frac{V_+ - 0}{2 \times 10^4} = 0$$

This yields two equations in three unknowns,  $V_{out}$ ,  $V_+$  and  $V_-$ . The third equation is the relationship between  $V_+$  and  $V_-$  for the ideal OPAMP,

$V_+=V_-$

Solving these equations, we find

$$V_{out} = 10V_{in} = 5\sin\omega t V$$

Since 2 k $\Omega$  resistor forms the load of the op-amp, then the current  $i_{out}$  is given by

$$i_{out} = \frac{V_{out}}{R_L} = \frac{5\sin\omega t}{2K\Omega} = 2.5\sin\omega t \ mA$$

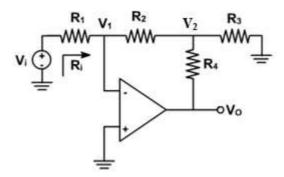

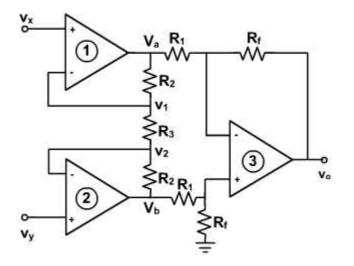

**Q.7.** For the different amplifier shown in figure 3.9 verify that  $V_o = -\left(1 + \frac{2R_2}{R_3}\right)\frac{R_f}{R_1}\left(V_x - V_y\right)$

Figure 3. 9 Circuit for Q.7

## Solution:

Since the differential input voltage of OPAMP is negligible, therefore,

$V_1 = V_x$ and  $V_2 = V_y$

The input impedance of OPAMP is very large and, therefore, the input current of OPAMP is negligible.

Thus

$$\frac{V_a - V_1}{R_2} = \frac{V_1 - V_2}{R_3}$$

$$\frac{V_a - V_x}{R_2} = \frac{V_x - V_y}{R_3}$$

$$V_a = \frac{R_2}{R_3} (V_x - V_y) + V_x$$

And

$$\frac{V_1 - V_2}{R_3} = \frac{V_2 - V_b}{R_2}$$

$$\frac{V_x - V_y}{R_3} = \frac{V_y - V_b}{R_2}$$

$$V_b = V_y - \frac{R_2}{R_3} \left( V_x - V_y \right)$$

The OPAMP3 is working as differential amplifier, therefore,

$$V_{o} = \frac{R_{f}}{R_{1}} (V_{b} - V_{a})$$

$$V_{o} = \frac{R_{f}}{R_{1}} \Big\{ V_{y} - V_{x} - 2\frac{R_{2}}{R_{3}} (V_{x} - V_{y}) \Big\}$$

$$V_{o} = -\Big(1 + \frac{2R_{2}}{R_{3}}\Big)\frac{R_{f}}{R_{1}} (V_{x} - V_{y})$$

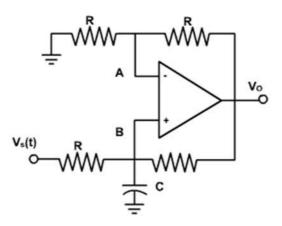

**Q.8.** Prove that the network shown in figure is a non-inverting integrator with.

$$V_o = \frac{2}{RC} \int V_s(t) dt$$

Figure 3. 10 Circuit for Q.8

## Solution:

The voltage at point A is  $V_0$  / 2 and it is also the voltage at point B because difference input voltage is negligible.

$V_B = V_O / 2$

Therefore, applying Node current equation at point B,

$$\frac{V_B - V_A}{R} + \frac{V_B - V_o}{R} + C \frac{dV_B}{dt} = 0$$

$$\frac{2V_B}{R} - \frac{V_s}{R} - \frac{V_o}{R} + C \frac{dV_B}{dt} = 0$$

$$\frac{V_o}{R} - \frac{V_s}{R} - \frac{V_o}{R} + \frac{C}{2} \frac{dV_o}{dt} = 0$$

$$\frac{dV_o}{dt} = \frac{2V_s}{RC}$$

$$V_o = \frac{2}{RC} \int V_s(t) dt$$

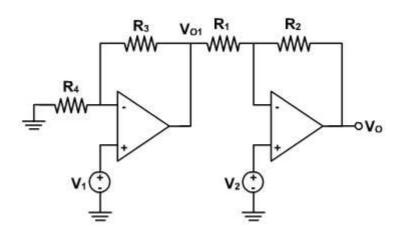

**Q.9.** For the circuit shown in figure 3.11 prove that  $V_o = \left(1 + \frac{R_2}{R_1}\right) \left(V_2 - \frac{1 + \frac{R_3}{R_4}}{1 + \frac{R_1}{R_2}}\right)$

Also verify that if  $R_3 / R_4 = R_1 / R_2$ , the circuit is an instrumentation amplifier with gain  $A = 1 + R_2 / R_1$ .

Figure 3. 11 Circuit for Q.9

Solution:

Here

$$V_{o1} = \left(1 + \frac{R_3}{R_4}\right) V_1$$

$$V_o = -\frac{R_2}{R_1} V_{o1} + \left(1 + \frac{R_2}{R_1}\right) V_2$$

$$V_{o} = -\frac{R_{2}}{R_{1}} \left(1 + \frac{R_{3}}{R_{4}}\right) V_{1} + \left(1 + \frac{R_{2}}{R_{1}}\right) V_{2}$$

$$V_{o} = \left(1 + \frac{R_{2}}{R_{1}}\right) \left(V_{2} - \frac{\frac{R_{2}}{R_{1}} \left(1 + \frac{R_{3}}{R_{4}}\right)}{\left(1 + \frac{R_{2}}{R_{1}}\right)} V_{1}\right)$$

$$V_{o} = \left(1 + \frac{R_{2}}{R_{1}}\right) \left(V_{2} - \frac{\left(1 + \frac{R_{3}}{R_{4}}\right)}{\left(1 + \frac{R_{3}}{R_{2}}\right)} V_{1}\right)$$

b). If  $\frac{R_3}{R_4} = \frac{R_1}{R_2}$  $V_o = \left(1 + \frac{R_2}{R_1}\right) \left(V_2 - \frac{\left(1 + \frac{R_1}{R_2}\right)}{\left(1 + \frac{R_1}{R_2}\right)}V_1\right)$  $V_o = \left(1 + \frac{R_2}{R_1}\right)(V_2 - V_1)$

So in this condition circuits as an instrument amplifier with gain  $\left(1 + \frac{R_2}{R_1}\right)$

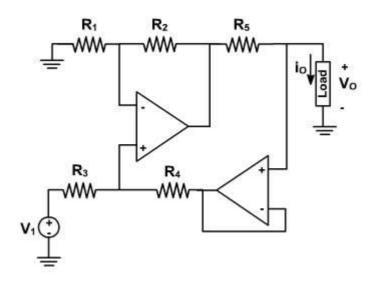

**Q.10.** Obtain an expression of the type  $i_0 = V_i / R - V_0 / R_0$  for the circuit shown in fig. 6. Hence verify that if  $R_4 / R_3 = R_2 / R_1$  the circuit is a V-I converter with  $R_0 = \infty$  and  $R = R_1 R_5 / R_2$ .

Figure 3. 12 Circuit for Q.10

Solution:

Here

$$V_{x} = V_{0} + \frac{V_{i} - V_{0}}{R_{3} + R_{4}} \cdot R_{4}$$

$$= V_{0} + \frac{V_{i}R_{4}}{R_{3} + R_{4}} - \frac{V_{0}R_{4}}{R_{3} + R_{4}}$$

$$= \frac{V_{i}R_{4}}{R_{3} + R_{4}} + \frac{V_{0}R_{3}}{R_{3} + R_{4}}$$

$$V_{01} = \left(1 + \frac{R_{2}}{R_{1}}\right) V_{x} = \frac{R_{4}}{R_{3} + R_{4}} \left(1 + \frac{R_{2}}{R_{1}}\right) V_{i} + \frac{R_{3}}{R_{3} + R_{4}} \left(1 + \frac{R_{2}}{R_{1}}\right) V_{0}$$

$i_0$  = current through the resistor.

$$= \frac{V_{01} - V_{0}}{R_{5}}$$

$$= \frac{R_{4}}{R_{5}(R_{3} + R_{4})} \left( 1 + \frac{R_{2}}{R_{1}} \right) V_{i} + \frac{R_{3}}{R_{5}(R_{3} + R_{4})} \left( 1 + \frac{R_{2}}{R_{1}} \right) V_{0} - \frac{V_{0}}{R_{5}}$$

$$= \frac{1 + (R_{2} / R_{1})}{R_{5} \left( 1 + \frac{R_{3}}{R_{4}} \right)} V_{i} + \frac{\left( 1 + \frac{R_{2}}{R_{1}} \right) V_{0}}{R_{5} \left( 1 + \frac{R_{4}}{R_{3}} \right)} - \frac{V_{0}}{R_{5}}$$

$$= \frac{V_{i}}{R} - \frac{V_{0}}{R_{0}}$$

Where

$$R = \frac{R_{5} \left(1 + \frac{R_{3}}{R_{4}}\right)}{\left(1 + \frac{R_{2}}{R_{1}}\right)}$$

$$R_{0} = \frac{R_{5}}{\frac{1 + R_{2}/R_{1}}{1 + R_{4}/R_{3}} - 1}$$

So when

$$\frac{R_4}{R_3} = \frac{R_2}{R_1}$$

then,

$$R = \frac{R_{5}\left(1 + \frac{R_{3}}{R_{4}}\right)}{\frac{R_{1}}{R_{2}}\left(1 + \frac{R_{2}}{R_{1}}\right)} = \frac{R_{5}R_{2}}{R_{1}}$$

$$R_{0} = \frac{R_{5}}{\frac{1 + R_{2}/R_{1}}{1 + R_{4}/R_{3}} - 1} = \frac{R_{5}}{1 - 1} \to \infty$$

# UNIT No 4

# ACTIVE FILTERS Of Operational Amplifier

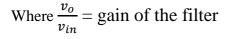

# **Q1.** *Draw the circuit of First order low pass filter and derive the expression for cut-off frequency* **Answer:**

First order low pass filter uses an RC network for filtering. Resistor  $R_1$  and  $R_F$  determine gain of the filter.

According to the voltage divider rule, voltage at the noninverting terminal is

$$v_1 = \frac{-jX_c}{R - jX_c} v_{in} \tag{1}$$

Where  $j = \sqrt{-1}$  and  $-jX_c = \frac{1}{j2\pi fC}$

Simplifying equation (1) we get

$$v_1 = \frac{v_{in}}{1 + j2\pi fRC}$$

And output voltage  $v_o = \left(1 + \frac{R_F}{R_1}\right) v_1$

That is

$$v_0 = \left(1 + \frac{R_F}{R_1}\right) \frac{v_{in}}{1 + j2\pi fRC}$$

Or

$$\frac{v_o}{v_{in}} = \frac{A_F}{1 + j(\frac{f}{f_H})}$$

Figure 4.1: First order low pass butterworth filter circuit

The gain angd phase angle equation of low pass filter can be obtained as

$$\left|\frac{v_0}{v_{in}}\right| = \frac{A_F}{\sqrt{1 + \left(\frac{f}{f_H}\right)^2}}$$

$$\varphi = -tan^{-1}\left(\frac{f}{f_H}\right)$$

Where  $\boldsymbol{\phi}$  is phase angle in degrees.

The operation of low pass filter can be verified from the gain magnitude equation as

1. At very low frequencies , that is  $f < f_H$ ,

$$\begin{aligned} \left| \frac{v_0}{v_{in}} \right| &\cong A_F \end{aligned}$$

2. At  $f = f_H$ ,

$$\left| \frac{v_0}{v_{in}} \right| &\cong \frac{A_F}{\sqrt{2}} = 0.707 A_F \end{aligned}$$

3.  $f > f_H$ ,

Thus low pass filter has a constant gain  $A_F$  from 0 Hz to high cut off frequency  $f_{H}$ . At  $f_H$  the gain is 0.707  $A_F$  and after  $f_H$  it decreases at a constant rate with an increase in frequency. The frequency  $f = f_H$  is called cut off frequency because the gain of the filter at high frequency is down by 3 db from 0 Hz.

$\left|\frac{v_0}{v_{in}}\right| > A_F$

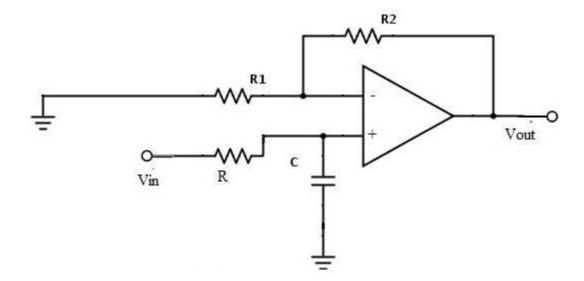

Q.2 Design a low cut off frequency of 1 kHz with a passband gain of 2.

#### Answer:

Select  $f_H = 1 \text{ kHz}$ .

Let C = 0.01 uF

$$R = \frac{1}{2\pi f_H C} = \frac{1}{2\pi (1k)(10^{-8})} = 15.9k\Omega$$

Since passband gain is 2,  $R_1$  and  $R_F$  must be equal .

Let  $R_1 = R_F = 10 \text{ k}\Omega$

Figure 4.2: Design of First order low pass butterworth filter circuit

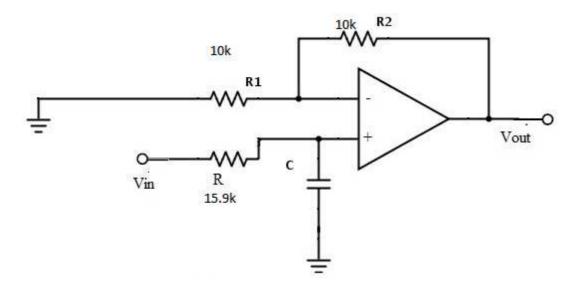

**Q.3** Draw the circuit of second order high pass filter and derive the expression for cut-off requency show that the gain roll off rate in stop band is 40db/decade.

Answer:

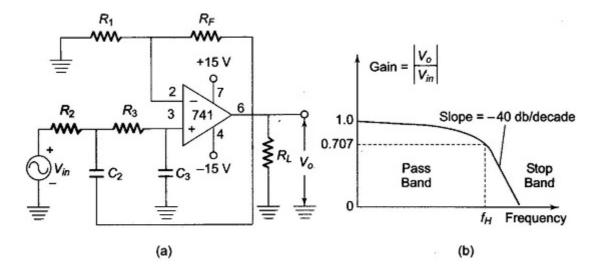

**Figure 4.3** : (a) second order low pass butterworth filter circuit (b) second order low pass butterworth filter frequency responce

A first order low pass filter can be converted into a second order type simply by using an additional RC network. Second order filter are important because higher order filters can be designed using them. the gain of second order filter is set by  $R_1$  and  $R_F$  while high cutoff frequency  $f_H$  is determined by  $R_2$ ,  $C_2$ ,  $R_3$ ,  $C_3$  as follows

$$f_H = \frac{1}{2\pi\sqrt{R_2R_3C_2C_3}}$$

In the circuit all the components and the circuit parameters are expressed in the S domain where S = jw.

Writing Kirchoff's current law at node  $V_A(S)$ ,

$$I_1 = I_2 + I_3$$

Or

$$\frac{V_{in} - V_A}{R_2} = \frac{V_A - V_0}{\frac{1}{SC_2}} + \frac{V_A - V_0}{R_3}$$

(1)

For simplicity in this equation omit S ,Applying voltage divider rule

$$V_1 = \frac{\frac{1}{SC_3}}{R_3 + \left(\frac{1}{SC_3}\right)} V_A$$

Since  $R_{iF} \cong \propto$ ,  $I_B \cong 0A$

$$V_1 = \frac{V_A}{R_3 C_3 S + 1}$$

Or

$$V_A = (R_3 C_3 S + 1) V_1$$

Substituting value of  $V_A$  in equation (1) and solving for  $V_1$  we get

$$V_1 = \frac{(R_3)(V_{in}) + (R_3R_2C_{2S})(V_0)}{(R_3C_3S + 1)(R_2 + R_3 + R_2R_3C_2S) - R_2}$$

However  $V_0 = (A_F)V_1$

Where  $A_F = 1 + \left(\frac{R_F}{R_1}\right)$

Therefore

$$V_0 = \frac{(A_F)(R_3)(V_{in}) + (R_3R_2C_{2S})(V_0)}{(R_3C_3S + 1)(R_2 + R_3 + R_2R_3C_2S) - R_2}$$

Solving this equation for  $\frac{v_0}{v_{in}}$  we have

$$\frac{v_0}{v_{in}} = \frac{A_F}{S^2 + \frac{(R_3C_3 + R_2C_3 + R_2C_2 - A_FR_2C_2)S}{R_2R_3C_2C_3} + \frac{1}{R_2R_3C_2C_3}}$$

For frequencies above  $f_H$  the gain of the second order low pass filter rolls off at the rate of -40 dB per decade. This means that

$$(w_H)^2 = \frac{1}{R_2 R_3 C_2 C_3}$$

Or

$$w_{H} = \frac{1}{\sqrt{R_{2}R_{3}C_{2}C_{3}}}$$

$$f_{H} = \frac{1}{2\pi\sqrt{R_{2}R_{3}C_{2}C_{3}}}$$

For the second order low pass butterworth response voltage gain magnitude equation is

$$\left. \frac{v_0}{v_{in}} \right| = \frac{A_F}{\sqrt{1 + \left(\frac{f}{f_H}\right)^4}}$$

Where  $A_F = 1 + \left(\frac{R_F}{R_1}\right) =$  pass band gain of the filter

f= frequency of input signal(Hz)

$f_H = \frac{1}{2\pi\sqrt{R_2R_3C_2C_3}} = \text{high cutoff frequency}$

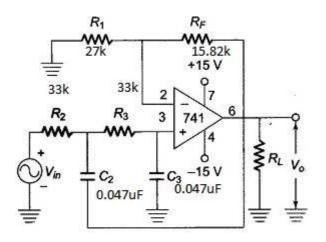

Q. 4 Design a second order low pass filter at a high cut off frequency of 1 kHz.

Answer:

$f_H = 1 \text{ kHz}$

Let  $C_2 = C_3 = 0.047 \mu F$

$$R_2 = R_3 = \frac{1}{(2\pi)(10^3)(47)(10^{-10})} = 33.86k\Omega$$

$R_F$  must be 0.586  $R_1$  ,let  $R_1{=}27k\Omega$  ,therefore

$$R_F = (0.586)(27k) = 15.82k\Omega$$

Figure 4.4:Design of second order low pass filter

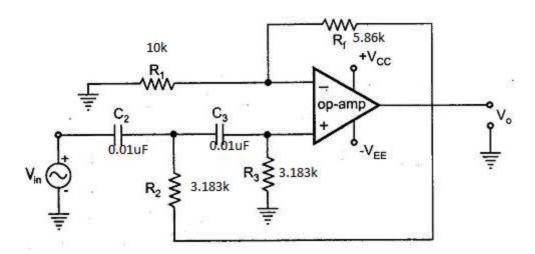

Que.5 . Design second order High-pass filter with cut-off frequency 5 KHz Ans.  $f_L {=}~5 \rm kHz$

Let  $C_2 = C_3 = 0.01 \mu F$

$$R2 = R3 = \frac{1}{2\pi f_L C} = \frac{1}{2\pi (5k)(10^{-8})} = 3.183k\Omega$$

Gain component  $R_1$  and  $R_F$ ,

Damping coefficient  $\alpha = 3$ -A<sub>F</sub> = 1.414

$A_{F} = 1.586$

$$A_F = 1 + \left(\frac{R_F}{R_1}\right)$$

Let  $R_1 = 10k\Omega$ , therefore  $R_F = 5.86k\Omega$

Figure 4.5:Design of second order high pass filter

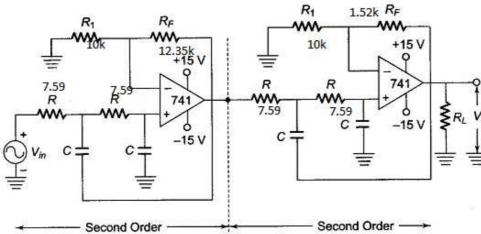

${\bf Q.6}$  . Design a fourth order Butter worth low-pass filter whose band width is 20 KHz. Use all capacitors of 1000 nf.

#### Answer:

$f_H=20 \text{ kHz}$

Let C= 1000nF,

For fourth order equation is  $(S^2 + 0.765S + 1)(S^2 + 1.848S + 1)$

$$R = \frac{1}{2\pi f_H C} = \frac{1}{2\pi (20k)(1000)(10^{-9})} = 7.59\Omega$$

For gain

**Stage 1**:  $\alpha_1 = 0.765$

$\alpha_1 = 3$ -  $A_{F1} = 0.765$

$$A_{FI} = 2.235$$

$$A_{F} = 1 + {\binom{R_{F}}{R_{1}}} = 2.235$$

Let  $R_{1} = 10k\Omega$ ,  $R_{F} = 12.35k\Omega$

**Stage 2**:  $\alpha_{1} = 1.848$

$\alpha_{1} = 3 - A_{FI} = 1.848$

$A_{FI} = 1.152$

$$A_{F} = 1 + {\binom{R_{F}}{R_{1}}} = 1.152$$

Let  $R_{1} = 10k\Omega$ ,  $R_{F} = 1.52k\Omega$

$$\prod_{\substack{R_{1} \\ R_{2} \\ R_{1} \\ R_{2} \\ R_{2} \\ R_{2} \\ R_{3} \\ R_{4} \\ R_{5} \\ R_$$

Figure 4.6: Design of fourth order Butter worth low-pass filter

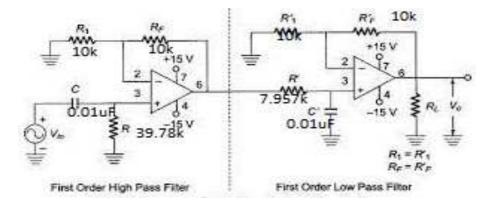

Q.7 Design first order wide-band pass filter with  $f_L = 400 Hz$  &  $f_H = 2 \mbox{ KHz}$

### Answer:

$f_L = 400 Hz \ \& \ f_H = 2 \ KHz$

$$A_{F1} * A_{F2} = 4$$

# First order low pass filter frequency component:

$f_H = 2 \text{ kHz}.$

Let C = 0.01 uF

$$R = \frac{1}{2\pi f_H C} = \frac{1}{2\pi (1k)(10^{-8})} = 7.957k\Omega$$

Since passband gain is 2,  $R_1$  and  $R_F$  must be equal .

Let  $R_1 = R_F = 10 \text{ k}\Omega$

# First order high pass filter frequency component:

$F_L = 400 \text{ Hz}.$

Let C = 0.01 uF

$$R' = \frac{1}{2\pi f_L C} = \frac{1}{2\pi (400)(10^{-8})} = 39.788k\Omega$$

Since passband gain is 2,  $R_1$  and  $R_F$  must be equal .

Let  $R_1$ '=  $R_F$ ' = 10 k $\Omega$

Figure 4.7: Design of first order wide-band pass filter

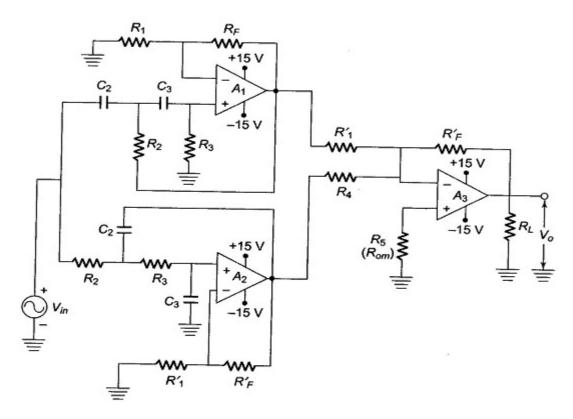

**Q.8** Design Second order wide-band reject filter with  $f_L = 4$  KHz &  $f_H = 1$  KHz.

Answer: Second order low pass filter:

$f_{\rm H} = 1 \ KHz$

Let C = 0.01 uF

$$R = \frac{1}{2\pi f_H C} = \frac{1}{2\pi (1k)(10^{-8})} = 15.915k\Omega$$

$C_1, C_2 = 0.01 uF$

$R_2, R_3 = 15.915 k\Omega$

Second order High pass filter:

$F_L = 4 \text{ kHz}.$

Let C = 0.01 uF

$$R' = \frac{1}{2\pi f_L C} = \frac{1}{2\pi (4k)(10^{-8})} = 3.9788k\Omega$$

C<sub>1</sub>',C<sub>2</sub> '= 0.01uF

$R_2', R_3' = 3.978 \text{ k}\Omega$ , Gain component of second order low pass and high pass filter:

$S^2 + 1.414S + 1$

$$\alpha = 1.414 = 3 - A_F$$

$$A_F = 1.586$$

Let  $R_1{=}\,R_1\,\dot{=}{10}{\rm k}\Omega$  ,  $R_F{=}\,R_F\,\dot{=}\,5.86{\rm k}\Omega$

For adder all resistance of 10 k $\Omega$  each.

Figure 4.8: Design of Second order wide-band reject filter

#### BOOK TITLE

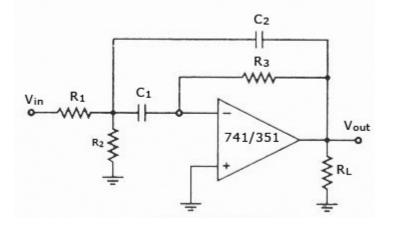

**Q** 9.Design narrow band pass filter shown in figure so that fc=1 kHz,Q=3, and  $A_F=10$ . Answer: Let  $C_1 = C_2 = C = 0.01$ uF.

$$R_{1} = \frac{Q}{2\pi f_{c}CA_{F}}$$

$$R_{1} = \frac{3}{(2\pi)(10^{3})(10^{-8})(10)} = 4.77k\Omega$$

$$R_{2} = \frac{Q}{2\pi f_{c}(2Q^{2} - A_{F})}$$

$$R_{2} = \frac{3}{(2\pi)(10^{3})(10^{-8})[2(3)^{2} - 10]} = 5.97k\Omega$$

Figure 4.9: Design of narrow band pass filter

$$R_3 = \frac{Q}{\pi f_c C}$$

$$R_3 = \frac{3}{(\pi)(10^3)(10^{-8})} = 95.5k\Omega$$

Use  $R_1 = 4.7 k\Omega$ ,  $R_2 = 6.2 k\Omega$  and  $R_3 = 100 k\Omega$ .

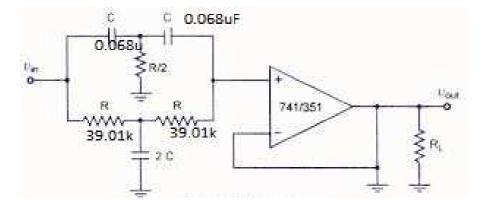

**Q.10** Design a 60 Hz active notch filter.

#### Answer:

Let C= 0.068uF

$$R = \frac{1}{2\pi f_N C} = \frac{1}{(2\pi)(60)(68)(10^{-9})} = 30.01k\Omega$$

For R/2 parallel two 39 k $\Omega$  resistors for the 2C component parallel two 0.068uF capacitors.

Figure 4.10: Design of active notch filter

# Unit-5

# Nonlinear Circuits And Waveform Generators

**Q.1.** Draw the circuit of Active Clipper and explain its working with waveforms.

#### Answer:

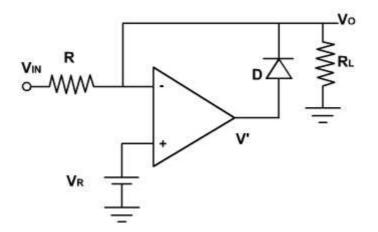

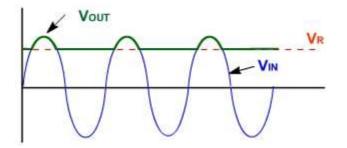

By slightly modifying the circuit, an active diode ideal clipper circuit is obtained Figure 5.1, shows an active clipper which clips the input voltage below  $V_R$ .

Figure 5. 1 Active Clipper using OP-AMP

When Vin  $\langle V_R \rangle$ , then v' is positive and D conducts. Under these conditions, the OPAMP works as a buffer and the output voltage equals the voltage at non-inverting terminal

Vout =  $V_R$ .

If Vin>  $V_R$ , then v' is negative and D is OFF and  $V_O = Vin R_L / (R_L + R) \gg Vi$  if R <<  $R_L$  Thus,

output follows input for Vin > V<sub>R</sub> and v<sub>O</sub> is clamped to V<sub>R</sub>if vin < V<sub>R</sub> by about 60 mV. **Figure 5.2**, shows the output waveform of clipper circuit. When D is reverse biased a large differential voltage may appear between inputs and the OPAMP must be capable to withstand this voltage.

Figure 5. 2 The output waveform of Clipper circuit

#### **Q.2.** Draw the circuit of Active Clamper and explain its working with waveforms.

#### Answer:

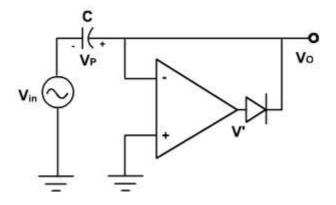

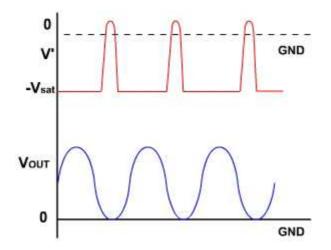

Figure 5.3 shows an active positive clamper circuit.

Figure 5. 3 Active Positive Clamper Circuit

The first negative half cycle produces a positive OPAMP output, which turns ON the diode. This capacitor charges to the peak of the input with the polarity shown in **Figure 5.3.** Just beyond the

80

#### BOOK TITLE

negative peak the diode turns off, the feedback loop opens, and the virtual ground is lost. Therefore,

$V_{\text{out}} = V_{\text{in}} + V_{\text{P}}$

Since  $V_P$  is being added to a sinusoidal voltage, the final output waveform is shifted positively through  $V_P$  volts. The output wave form swing from 0 to  $2V_P$  as shows in **Figure 5.4.** Again the reduction of the diode-offset voltage allows clamping with low-level inputs.

During most of the cycle, the OPAMP operates in negative saturation. Right at the negative input peak, the OPAMP produces a sharp positive going pulse that replaces any change lost by the clamping capacitor between negative input peaks.

Figure 5. 4 Output Waveforms of Active Positive Clamper

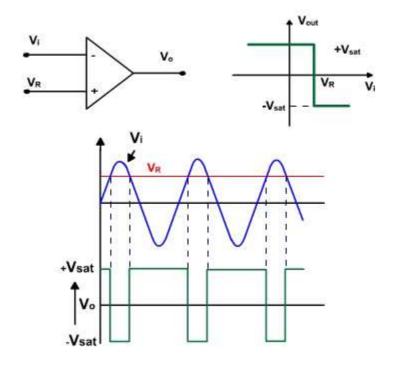

#### Q.3. Draw the circuit of Comparator and explain its working with related waveforms.

#### Answer:

An analog comparator has two inputs one is usually a constant reference voltage  $V_R$  and other is a time varying signal  $V_i$  and one output  $V_0$ . The basic circuit of a comparator is shown in **Figure 5.5**.

#### BOOK TITLE

When the noninverting voltage is larger than the inverting voltage the comparator produces a high output voltage  $(+V_{sat})$ . When the non-inverting output is less than the inverting input the output is low  $(-V_{sat})$ . **Figure 5.5**, also shows the output of a comparator for a sinusoidal.

Figure 5. 5 Basic Comparator and its output waveform

$$V_0 = -V_{sat}$$

if  $V_i > V_R$

$$= + V_{sat}$$

if  $V_i < V_R$

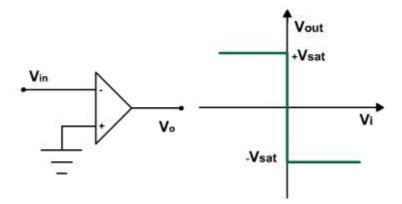

If  $V_R = 0$ , then slightest input voltage (in mV) is enough to saturate the OPAMP and the circuit acts as zero crossing detector as shown in **Figure 5.6**. If the supply voltages are ±15V, then the output compliance is from approximate – 13V to +13V. The more the open loop gain of OPAMP, the smaller the voltage required to saturate the output. If v<sub>d</sub>required is very small then the characteristic is a vertical line as shown in **Figure 5.6**.

Figure 5. 6 Zero crossing detector

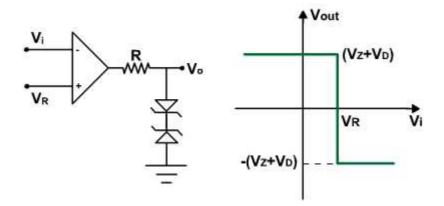

If we want to limit the output voltage of the comparator two voltages (one positive and other negative) then a resistor R and two zener diodes are added to clamp the output of the comparator. The circuit of such comparator is shown in **Figure 5.7**, The transfer characteristics of the circuit is also shown in **Figure 5.7**.

Figure 5.7 Comparator with limiting output using zener diode

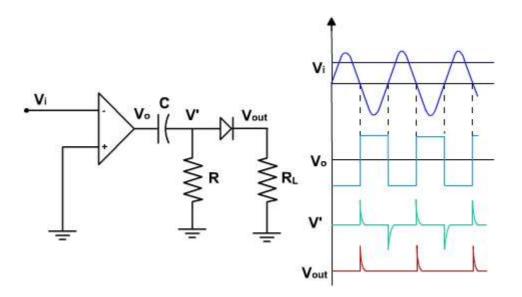

The resistance is chosen so that the zener operates in zener breakdown region. When  $V_R=0$  then the output changes rapidly from one state to other very rapidly every time that the input passes through zero as shown in **Figure 5.8**

Figure 5. 8 Zero crossing detector

Such a configuration is called zero crossing detector. If we want pulses at zero crossing then a differentiator and a series diode is connected at the output. It produces single pulses at the zero crossing point in every cycle.

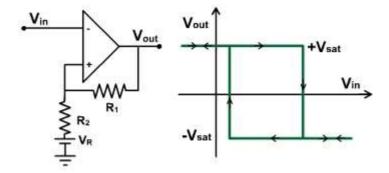

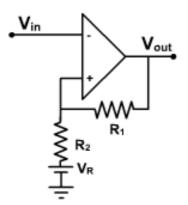

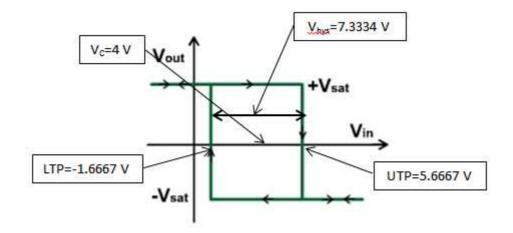

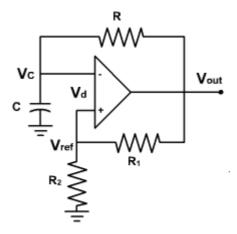

**Q.4.** Draw the circuit of Inverting Schmitt Trigger and explain its working. Also explain how the hysteresis curve can be shifted on x-axis.

#### Answer:

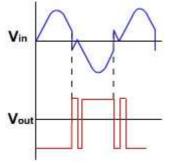

If the input to a comparator contains noise, the output may be erractive when  $v_{in}$  is near a trip point. For instance, with a zero crossing, the output is low when  $v_{in}$  is positive and high when  $v_{in}$  is negative. If the input contains a noise voltage with a peak of 1mV or more, then the comparator will detect the zero crossing produced by the noise **Figure 5.9** shows the output of zero crossing detection if the input contains noise.

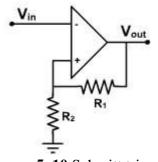

Figure 5. 10 Schmitt trigger

Figure 5. 9 Zero crossing detector output with noise

This can be avoided by using a Schmitt trigger, circuit which is basically a comparator with positive feedback. **Figure 5.10**, shows an inverting Schmitt trigger circuit using OPAMP.

Because of the voltage divider circuit, there is a positive feedback voltage. When OPAMP is positively saturated, a positive voltage is feedback to the non-inverting input, this positive voltage holds the output in high stage. ( $V_{in} < V_f$ ). When the output voltage is negatively saturated, a negative voltage feedback to the inverting input, holding the output in low state.

When the output is  $+V_{sat}$  then reference voltage  $V_{ref}$  is given by

$$V_{ref} = \left(\frac{R_2}{R_1 + R_2}\right) \times (+V_{sat}) = +\beta V_{sat}$$

If  $V_{in}$  is less than  $V_{ref}$  output will remain  $+V_{sat}$ .

When input  $V_{in}$  exceeds  $V_{ref} = +V_{sat}$  the output switches from  $+V_{sat}$  to  $-V_{sat}$ . Then the reference voltage is given by

$$V_{ref} = \left(\frac{R_2}{R_1 + R_2}\right) \times (-V_{sat}) = -\beta V_{sat}$$

The output will remain  $-V_{sat}$  as long as  $v_{in}>V_{ref}$ .

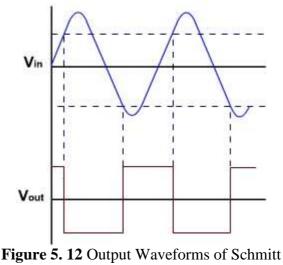

trigger

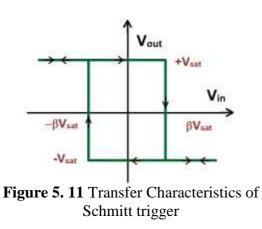

If  $V_{in} < V_{ref}$  i.e.  $V_{in}$  becomes more negative than  $-V_{sat}$  then again output switches to  $+V_{sat}$  and so on. The transfer characteristic of Schmitt trigger circuit is shown in **Figure 5.11**. The output is also shown in **Figure 5.12** for a sinusoidal wave. If the input is different than sine even then the output will be determined in a same way.

Positive feedback has an unusual effect on the circuit. It forces the reference voltage to have the same polarity as the output voltage, The reference. voltage is positive when the output voltage is high (+Vsat) and negative when the output is low (-Vsat).

In a Schmitt trigger, the voltages at which the output switches from +vsat to –vsat or vice versa are called upper trigger point (UTP) and lower trigger point (LTP). the difference between the two trip points is called hysteresis.

$$UTP = \left(\frac{R_2}{R_1 + R_2}\right) \times (+V_{sat}) = +\beta V_{sat}$$

$$LTP = \left(\frac{R_2}{R_1 + R_2}\right) \times (-V_{sat}) = -\beta V_{sat}$$

BOOK TITLE

$$V_{hys} = UTP - LTP$$

$$V_{hys} = \left(\frac{R_2}{R_1 + R_2}\right) \times (+V_{sat}) - \left(\frac{R_2}{R_1 + R_2}\right) \times (-V_{sat})$$

$$V_{hys} = 2\left(\frac{R_2}{R_1 + R_2}\right) V_{sat}$$

$$V_{hys} = 2\beta V_{sat}$$

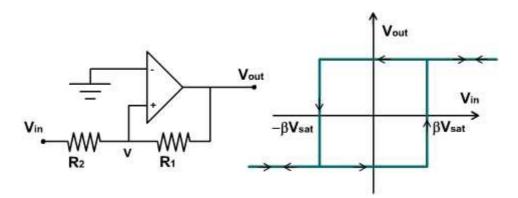

The hysteresis loop can be shifted to either side of zero point by connecting a voltage source as shown in **Figure 5.13**.

Figure 5. 13 Schmitt trigger with shifted Hysterisis curve

When  $V_0$ =+Vsat , the reference. Voltage (UTP) is given by

$$UTP = \left(\frac{R_2(+V_{sat} - V_R)}{R_1 + R_2}\right) + V_R$$

$$UTP = \beta V_{sat} + \left(\frac{R_1}{R_1 + R_2}V_R\right)$$

When  $V_0$ = -Vsat , the reference. Voltage (UTP) is given by

$$LTP = \left(\frac{R_2(-V_{sat} - V_R)}{R_1 + R_2}\right) + V_R$$

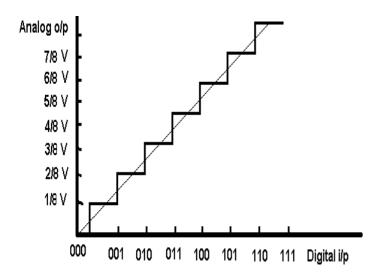

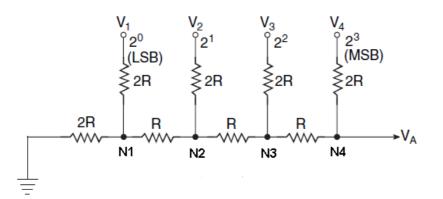

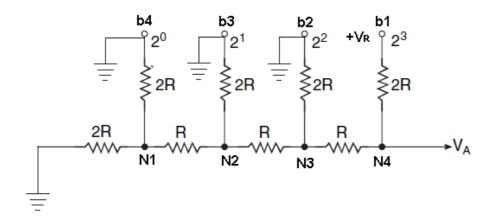

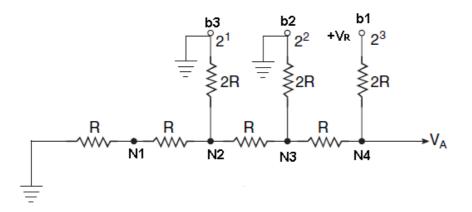

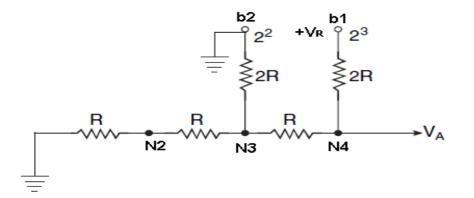

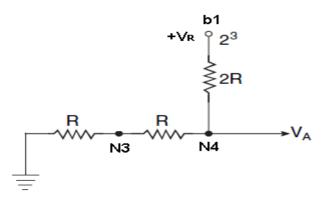

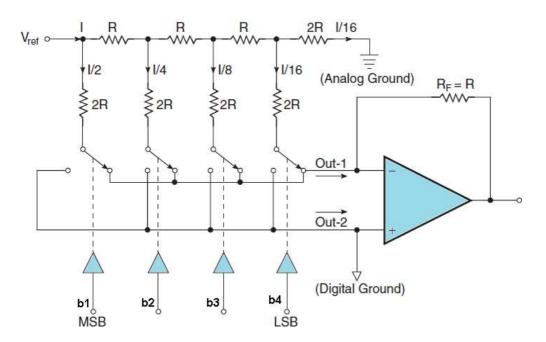

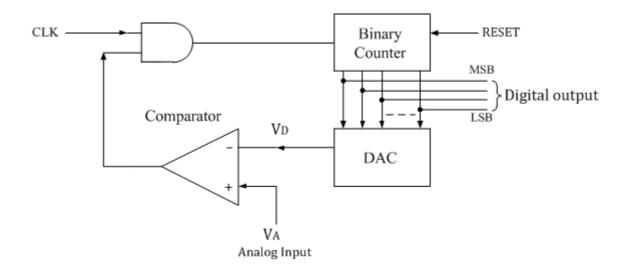

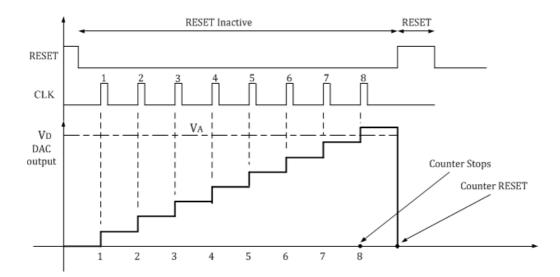

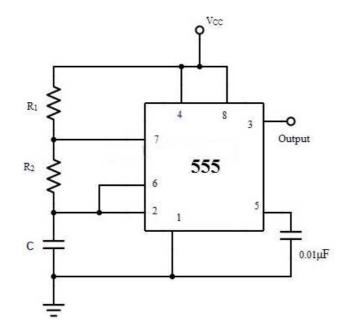

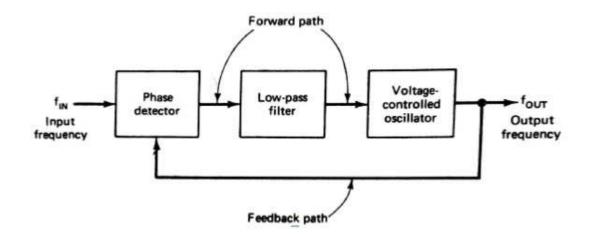

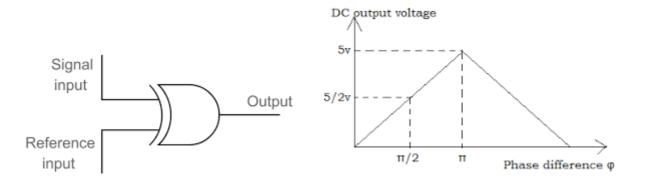

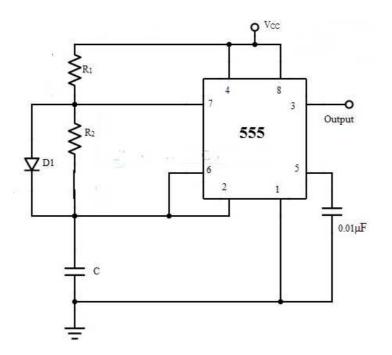

$$LTP = -\beta V_{sat} + \left(\frac{R_1}{R_1 + R_2}V_R\right)$$